|

AMC13

Firmwares for the different applications of the AMC13 uTCA board made at Boston University

|

|

AMC13

Firmwares for the different applications of the AMC13 uTCA board made at Boston University

|

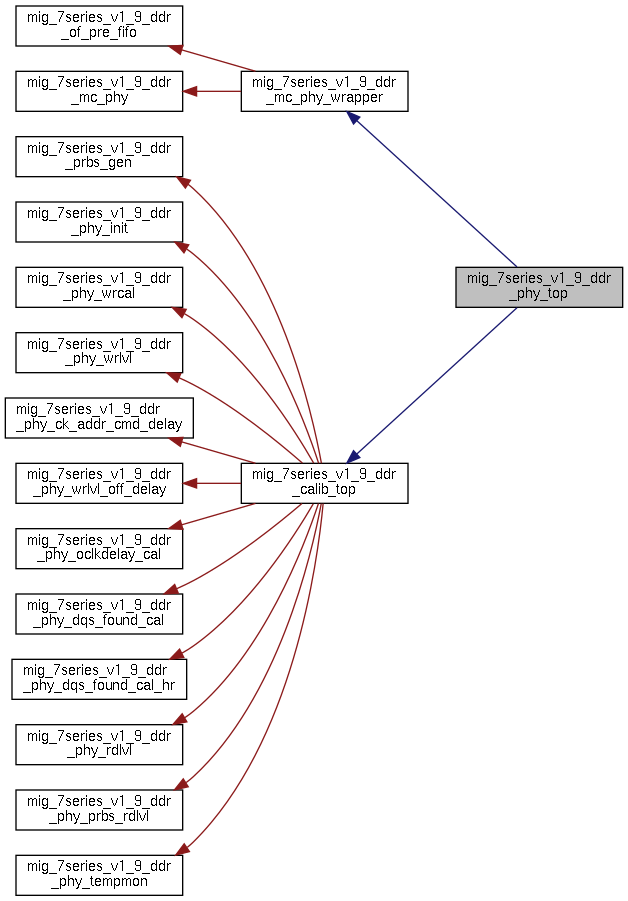

Entities | |

| arch_ddr_phy_top | architecture |

Use Clauses | |

| numeric_std | |

Generics | |

| TCQ | integer := 100 |

| AL | string := " 0 " |

| BANK_WIDTH | integer := 3 |

| BURST_MODE | string := " 8 " |

| BURST_TYPE | string := " SEQ " |

| CA_MIRROR | string := " OFF " |

| CK_WIDTH | integer := 1 |

| CL | integer := 5 |

| COL_WIDTH | integer := 12 |

| CS_WIDTH | integer := 1 |

| CKE_WIDTH | integer := 1 |

| CWL | integer := 5 |

| DM_WIDTH | integer := 8 |

| DQ_WIDTH | integer := 64 |

| DQS_CNT_WIDTH | integer := 3 |

| DQS_WIDTH | integer := 8 |

| DRAM_TYPE | string := " DDR3 " |

| DRAM_WIDTH | integer := 8 |

| MASTER_PHY_CTL | integer := 0 |

| LP_DDR_CK_WIDTH | integer := 2 |

| DATA_IO_IDLE_PWRDWN | string := " ON " |

| PHYCTL_CMD_FIFO | string := " FALSE " |

| DATA_CTL_B0 | std_logic_vector ( 3 downto 0 ) := X " c " |

| DATA_CTL_B1 | std_logic_vector ( 3 downto 0 ) := X " f " |

| DATA_CTL_B2 | std_logic_vector ( 3 downto 0 ) := X " f " |

| DATA_CTL_B3 | std_logic_vector ( 3 downto 0 ) := X " f " |

| DATA_CTL_B4 | std_logic_vector ( 3 downto 0 ) := X " f " |

| BYTE_LANES_B0 | std_logic_vector ( 3 downto 0 ) := " 1111 " |

| BYTE_LANES_B1 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| BYTE_LANES_B2 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| BYTE_LANES_B3 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| BYTE_LANES_B4 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| PHY_0_BITLANES | std_logic_vector ( 47 downto 0 ) := X " 000000000000 " |

| PHY_1_BITLANES | std_logic_vector ( 47 downto 0 ) := X " 000000000000 " |

| PHY_2_BITLANES | std_logic_vector ( 47 downto 0 ) := X " 000000000000 " |

| CK_BYTE_MAP | std_logic_vector ( 143 downto 0 ) := X " 000000000000000000000000000000000000 " |

| ADDR_MAP | std_logic_vector ( 191 downto 0 ) := X " 000000000000000000000000000000000000000000000000 " |

| BANK_MAP | std_logic_vector ( 35 downto 0 ) := X " 000000000 " |

| CAS_MAP | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| CKE_ODT_BYTE_MAP | std_logic_vector ( 7 downto 0 ) := X " 00 " |

| CKE_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| ODT_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| CKE_ODT_AUX | string := " FALSE " |

| CS_MAP | std_logic_vector ( 119 downto 0 ) := X " 000000000000000000000000000000 " |

| PARITY_MAP | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| RAS_MAP | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| WE_MAP | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| DQS_BYTE_MAP | std_logic_vector ( 143 downto 0 ) := X " 000000000000000000000000000000000000 " |

| DATA0_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA1_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA2_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA3_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA4_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA5_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA6_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA7_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA8_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA9_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA10_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA11_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA12_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA13_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA14_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA15_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA16_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA17_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| MASK0_MAP | std_logic_vector ( 107 downto 0 ) := X " 000000000000000000000000000 " |

| MASK1_MAP | std_logic_vector ( 107 downto 0 ) := X " 000000000000000000000000000 " |

| PRE_REV3ES | string := " OFF " |

| nCK_PER_CLK | integer := 2 |

| nCS_PER_RANK | integer := 1 |

| ADDR_CMD_MODE | string := " 1T " |

| IODELAY_HP_MODE | string := " ON " |

| BANK_TYPE | string := " HP_IO " |

| DATA_IO_PRIM_TYPE | string := " DEFAULT " |

| IODELAY_GRP | string := " IODELAY_MIG " |

| IBUF_LPWR_MODE | string := " OFF " |

| OUTPUT_DRV | string := " HIGH " |

| REG_CTRL | string := " OFF " |

| RTT_NOM | string := " 60 " |

| RTT_WR | string := " 120 " |

| tCK | integer := 2500 |

| tRFC | integer := 110000 |

| DDR2_DQSN_ENABLE | string := " YES " |

| WRLVL | string := " OFF " |

| DEBUG_PORT | string := " OFF " |

| RANKS | integer := 4 |

| ODT_WIDTH | integer := 1 |

| ROW_WIDTH | integer := 16 |

| SLOT_1_CONFIG | std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| CALIB_ROW_ADD | std_logic_vector ( 15 downto 0 ) := X " 0000 " |

| CALIB_COL_ADD | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| CALIB_BA_ADD | std_logic_vector ( 2 downto 0 ) := " 000 " |

| SIM_BYPASS_INIT_CAL | string := " OFF " |

| REFCLK_FREQ | real := 200 . 0 |

| USE_CS_PORT | integer := 1 |

| USE_DM_PORT | integer := 1 |

| USE_ODT_PORT | integer := 1 |

| RD_PATH_REG | integer := 0 |

Ports | |

| clk | in std_logic |

| clk_ref | in std_logic |

| freq_refclk | in std_logic |

| mem_refclk | in std_logic |

| pll_lock | in std_logic |

| sync_pulse | in std_logic |

| error | in std_logic |

| rst_tg_mc | out std_logic |

| device_temp | in std_logic_vector ( 11 downto 0 ) |

| tempmon_sample_en | in std_logic |

| dbg_sel_pi_incdec | in std_logic |

| dbg_sel_po_incdec | in std_logic |

| dbg_byte_sel | in std_logic_vector ( DQS_CNT_WIDTH downto 0 ) |

| dbg_pi_f_inc | in std_logic |

| dbg_pi_f_dec | in std_logic |

| dbg_po_f_inc | in std_logic |

| dbg_po_f_stg23_sel | in std_logic |

| dbg_po_f_dec | in std_logic |

| dbg_idel_down_all | in std_logic |

| dbg_idel_down_cpt | in std_logic |

| dbg_idel_up_all | in std_logic |

| dbg_idel_up_cpt | in std_logic |

| dbg_sel_all_idel_cpt | in std_logic |

| dbg_sel_idel_cpt | in std_logic_vector ( DQS_CNT_WIDTH - 1 downto 0 ) |

| rst | in std_logic |

| slot_0_present | in std_logic_vector ( 7 downto 0 ) |

| slot_1_present | in std_logic_vector ( 7 downto 0 ) |

| mc_ras_n | in std_logic_vector ( nCK_PER_CLK - 1 downto 0 ) |

| mc_cas_n | in std_logic_vector ( nCK_PER_CLK - 1 downto 0 ) |

| mc_we_n | in std_logic_vector ( nCK_PER_CLK - 1 downto 0 ) |

| mc_address | in std_logic_vector ( nCK_PER_CLK * ROW_WIDTH - 1 downto 0 ) |

| mc_bank | in std_logic_vector ( nCK_PER_CLK * BANK_WIDTH - 1 downto 0 ) |

| mc_cs_n | in std_logic_vector ( CS_WIDTH * nCS_PER_RANK * nCK_PER_CLK - 1 downto 0 ) |

| mc_reset_n | in std_logic |

| mc_odt | in std_logic_vector ( 1 downto 0 ) |

| mc_cke | in std_logic_vector ( nCK_PER_CLK - 1 downto 0 ) |

| mc_aux_out0 | in std_logic_vector ( 3 downto 0 ) |

| mc_aux_out1 | in std_logic_vector ( 3 downto 0 ) |

| mc_cmd_wren | in std_logic |

| mc_ctl_wren | in std_logic |

| mc_cmd | in std_logic_vector ( 2 downto 0 ) |

| mc_cas_slot | in std_logic_vector ( 1 downto 0 ) |

| mc_data_offset | in std_logic_vector ( 5 downto 0 ) |

| mc_data_offset_1 | in std_logic_vector ( 5 downto 0 ) |

| mc_data_offset_2 | in std_logic_vector ( 5 downto 0 ) |

| mc_rank_cnt | in std_logic_vector ( 1 downto 0 ) |

| mc_wrdata_en | in std_logic |

| mc_wrdata | in std_logic_vector ( 2 * nCK_PER_CLK * DQ_WIDTH - 1 downto 0 ) |

| mc_wrdata_mask | in std_logic_vector ( ( 2 * nCK_PER_CLK * ( DQ_WIDTH / 8 ) ) - 1 downto 0 ) |

| idle | in std_logic |

| ddr_addr | out std_logic_vector ( ROW_WIDTH - 1 downto 0 ) |

| ddr_ba | out std_logic_vector ( BANK_WIDTH - 1 downto 0 ) |

| ddr_cas_n | out std_logic |

| ddr_ck_n | out std_logic_vector ( CK_WIDTH - 1 downto 0 ) |

| ddr_ck | out std_logic_vector ( CK_WIDTH - 1 downto 0 ) |

| ddr_cke | out std_logic_vector ( CKE_WIDTH - 1 downto 0 ) |

| ddr_cs_n | out std_logic_vector ( ( CS_WIDTH * nCS_PER_RANK ) - 1 downto 0 ) |

| ddr_dm | out std_logic_vector ( DM_WIDTH - 1 downto 0 ) |

| ddr_odt | out std_logic_vector ( ODT_WIDTH - 1 downto 0 ) |

| ddr_ras_n | out std_logic |

| ddr_reset_n | out std_logic |

| ddr_parity | out std_logic |

| ddr_we_n | out std_logic |

| ddr_dq | inout std_logic_vector ( DQ_WIDTH - 1 downto 0 ) |

| ddr_dqs_n | inout std_logic_vector ( DQS_WIDTH - 1 downto 0 ) |

| ddr_dqs | inout std_logic_vector ( DQS_WIDTH - 1 downto 0 ) |

| dbg_calib_top | out std_logic_vector ( 255 downto 0 ) |

| dbg_cpt_first_edge_cnt | out std_logic_vector ( 6 * DQS_WIDTH * RANKS - 1 downto 0 ) |

| dbg_cpt_second_edge_cnt | out std_logic_vector ( 6 * DQS_WIDTH * RANKS - 1 downto 0 ) |

| dbg_cpt_tap_cnt | out std_logic_vector ( 6 * DQS_WIDTH * RANKS - 1 downto 0 ) |

| dbg_dq_idelay_tap_cnt | out std_logic_vector ( 5 * DQS_WIDTH * RANKS - 1 downto 0 ) |

| dbg_phy_rdlvl | out std_logic_vector ( 255 downto 0 ) |

| dbg_phy_wrcal | out std_logic_vector ( 99 downto 0 ) |

| dbg_final_po_fine_tap_cnt | out std_logic_vector ( 6 * DQS_WIDTH - 1 downto 0 ) |

| dbg_final_po_coarse_tap_cnt | out std_logic_vector ( 3 * DQS_WIDTH - 1 downto 0 ) |

| dbg_rd_data_edge_detect | out std_logic_vector ( DQS_WIDTH - 1 downto 0 ) |

| dbg_rddata | out std_logic_vector ( 2 * nCK_PER_CLK * DQ_WIDTH - 1 downto 0 ) |

| dbg_rddata_valid | out std_logic |

| dbg_rdlvl_done | out std_logic_vector ( 1 downto 0 ) |

| dbg_rdlvl_err | out std_logic_vector ( 1 downto 0 ) |

| dbg_rdlvl_start | out std_logic_vector ( 1 downto 0 ) |

| dbg_tap_cnt_during_wrlvl | out std_logic_vector ( 5 downto 0 ) |

| dbg_wl_edge_detect_valid | out std_logic |

| dbg_wrlvl_done | out std_logic |

| dbg_wrlvl_err | out std_logic |

| dbg_wrlvl_start | out std_logic |

| dbg_wrlvl_fine_tap_cnt | out std_logic_vector ( 6 * DQS_WIDTH - 1 downto 0 ) |

| dbg_wrlvl_coarse_tap_cnt | out std_logic_vector ( 3 * DQS_WIDTH - 1 downto 0 ) |

| dbg_phy_wrlvl | out std_logic_vector ( 255 downto 0 ) |

| dbg_pi_phaselock_start | out std_logic |

| dbg_pi_phaselocked_done | out std_logic |

| dbg_pi_phaselock_err | out std_logic |

| dbg_pi_phase_locked_phy4lanes | out std_logic_vector ( 11 downto 0 ) |

| dbg_pi_dqsfound_start | out std_logic |

| dbg_pi_dqsfound_done | out std_logic |

| dbg_pi_dqsfound_err | out std_logic |

| dbg_pi_dqs_found_lanes_phy4lanes | out std_logic_vector ( 11 downto 0 ) |

| dbg_wrcal_start | out std_logic |

| dbg_wrcal_done | out std_logic |

| dbg_wrcal_err | out std_logic |

| phy_mc_ctl_full | out std_logic |

| phy_mc_cmd_full | out std_logic |

| phy_mc_data_full | out std_logic |

| init_calib_complete | out std_logic |

| init_wrcal_complete | out std_logic |

| calib_rd_data_offset_0 | out std_logic_vector ( 6 * RANKS - 1 downto 0 ) |

| calib_rd_data_offset_1 | out std_logic_vector ( 6 * RANKS - 1 downto 0 ) |

| calib_rd_data_offset_2 | out std_logic_vector ( 6 * RANKS - 1 downto 0 ) |

| phy_rddata_valid | out std_logic |

| phy_rd_data | out std_logic_vector ( 2 * nCK_PER_CLK * DQ_WIDTH - 1 downto 0 ) |

| ref_dll_lock | out std_logic |

| rst_phaser_ref | in std_logic |

| dbg_rd_data_offset | out std_logic_vector ( 6 * RANKS - 1 downto 0 ) |

| dbg_phy_init | out std_logic_vector ( 255 downto 0 ) |

| dbg_prbs_rdlvl | out std_logic_vector ( 255 downto 0 ) |

| dbg_dqs_found_cal | out std_logic_vector ( 255 downto 0 ) |

| dbg_pi_counter_read_val | out std_logic_vector ( 5 downto 0 ) |

| dbg_po_counter_read_val | out std_logic_vector ( 8 downto 0 ) |

| dbg_oclkdelay_calib_start | out std_logic |

| dbg_oclkdelay_calib_done | out std_logic |

| dbg_phy_oclkdelay_cal | out std_logic_vector ( 255 downto 0 ) |

| dbg_oclkdelay_rd_data | out std_logic_vector ( DRAM_WIDTH * 16 - 1 downto 0 ) |

Additional Inherited Members |

Definition at line 73 of file mig_7series_v1_9_ddr_phy_top.vhd.

1.8.1

1.8.1