|

AMC13

Firmwares for the different applications of the AMC13 uTCA board made at Boston University

|

|

AMC13

Firmwares for the different applications of the AMC13 uTCA board made at Boston University

|

Entities | |

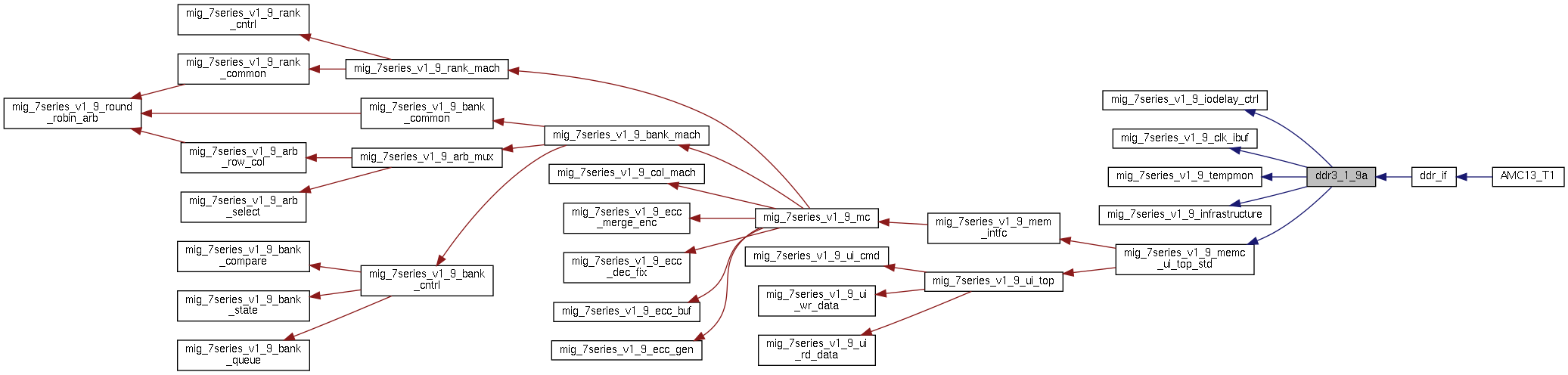

| arch_ddr3_1_9a | architecture |

Use Clauses | |

| numeric_std | |

Generics | |

| BANK_WIDTH | integer := 3 |

| CK_WIDTH | integer := 1 |

| COL_WIDTH | integer := 10 |

| CS_WIDTH | integer := 1 |

| nCS_PER_RANK | integer := 1 |

| CKE_WIDTH | integer := 1 |

| DATA_BUF_ADDR_WIDTH | integer := 5 |

| DQ_CNT_WIDTH | integer := 5 |

| DQ_PER_DM | integer := 8 |

| DM_WIDTH | integer := 4 |

| DQ_WIDTH | integer := 32 |

| DQS_WIDTH | integer := 4 |

| DQS_CNT_WIDTH | integer := 2 |

| DRAM_WIDTH | integer := 8 |

| ECC | string := " OFF " |

| DATA_WIDTH | integer := 32 |

| ECC_TEST | string := " OFF " |

| PAYLOAD_WIDTH | integer := 32 |

| ECC_WIDTH | integer := 8 |

| MC_ERR_ADDR_WIDTH | integer := 31 |

| MEM_ADDR_ORDER | string := " BANK_ROW_COLUMN " |

| nBANK_MACHS | integer := 4 |

| RANKS | integer := 1 |

| ODT_WIDTH | integer := 1 |

| ROW_WIDTH | integer := 14 |

| ADDR_WIDTH | integer := 28 |

| USE_CS_PORT | integer := 0 |

| USE_DM_PORT | integer := 1 |

| USE_ODT_PORT | integer := 1 |

| PHY_CONTROL_MASTER_BANK | integer := 1 |

| MEM_DENSITY | string := " 2Gb " |

| MEM_SPEEDGRADE | string := " 107E " |

| MEM_DEVICE_WIDTH | integer := 16 |

| AL | string := " 0 " |

| nAL | integer := 0 |

| BURST_MODE | string := " 8 " |

| BURST_TYPE | string := " SEQ " |

| CL | integer := 13 |

| CWL | integer := 9 |

| OUTPUT_DRV | string := " LOW " |

| RTT_NOM | string := " 60 " |

| RTT_WR | string := " OFF " |

| ADDR_CMD_MODE | string := " 1T " |

| REG_CTRL | string := " OFF " |

| CA_MIRROR | string := " OFF " |

| CLKIN_PERIOD | integer := 4288 |

| CLKFBOUT_MULT | integer := 8 |

| DIVCLK_DIVIDE | integer := 1 |

| CLKOUT0_PHASE | real := 337 . 5 |

| CLKOUT0_DIVIDE | integer := 2 |

| CLKOUT1_DIVIDE | integer := 2 |

| CLKOUT2_DIVIDE | integer := 32 |

| CLKOUT3_DIVIDE | integer := 8 |

| tCKE | integer := 5000 |

| tFAW | integer := 25000 |

| tPRDI | integer := 1000000 |

| tRAS | integer := 34000 |

| tRCD | integer := 13910 |

| tREFI | integer := 7800000 |

| tRFC | integer := 160000 |

| tRP | integer := 13910 |

| tRRD | integer := 5000 |

| tRTP | integer := 7500 |

| tWTR | integer := 7500 |

| tZQI | integer := 128000000 |

| tZQCS | integer := 64 |

| SIM_BYPASS_INIT_CAL | string := " OFF " |

| SIMULATION | string := " FALSE " |

| BYTE_LANES_B0 | std_logic_vector ( 3 downto 0 ) := " 0011 " |

| BYTE_LANES_B1 | std_logic_vector ( 3 downto 0 ) := " 1111 " |

| BYTE_LANES_B2 | std_logic_vector ( 3 downto 0 ) := " 1100 " |

| BYTE_LANES_B3 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| BYTE_LANES_B4 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| DATA_CTL_B0 | std_logic_vector ( 3 downto 0 ) := " 0011 " |

| DATA_CTL_B1 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| DATA_CTL_B2 | std_logic_vector ( 3 downto 0 ) := " 1100 " |

| DATA_CTL_B3 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| DATA_CTL_B4 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| PHY_0_BITLANES | std_logic_vector ( 47 downto 0 ) := X " 00000037F2FF " |

| PHY_1_BITLANES | std_logic_vector ( 47 downto 0 ) := X " 000004F3FDFF " |

| PHY_2_BITLANES | std_logic_vector ( 47 downto 0 ) := X " 3FE3DF000000 " |

| CK_BYTE_MAP | std_logic_vector ( 143 downto 0 ) := X " 000000000000000000000000000000000013 " |

| ADDR_MAP | std_logic_vector ( 191 downto 0 ) := X " 00000010610710A10210510811B10110010B111113122119 " |

| BANK_MAP | std_logic_vector ( 35 downto 0 ) := X " 11510311A " |

| CAS_MAP | std_logic_vector ( 11 downto 0 ) := X " 118 " |

| CKE_ODT_BYTE_MAP | std_logic_vector ( 7 downto 0 ) := X " 00 " |

| CKE_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000104 " |

| ODT_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000112 " |

| CS_MAP | std_logic_vector ( 119 downto 0 ) := X " 000000000000000000000000000000 " |

| PARITY_MAP | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| RAS_MAP | std_logic_vector ( 11 downto 0 ) := X " 110 " |

| WE_MAP | std_logic_vector ( 11 downto 0 ) := X " 114 " |

| DQS_BYTE_MAP | std_logic_vector ( 143 downto 0 ) := X " 000000000000000000000000000000012223 " |

| DATA0_MAP | std_logic_vector ( 95 downto 0 ) := X " 232235237234238231236233 " |

| DATA1_MAP | std_logic_vector ( 95 downto 0 ) := X " 220226221224223227228229 " |

| DATA2_MAP | std_logic_vector ( 95 downto 0 ) := X " 012015013016018011014019 " |

| DATA3_MAP | std_logic_vector ( 95 downto 0 ) := X " 000002001009006003005007 " |

| DATA4_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA5_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA6_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA7_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA8_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA9_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA10_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA11_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA12_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA13_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA14_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA15_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA16_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| DATA17_MAP | std_logic_vector ( 95 downto 0 ) := X " 000000000000000000000000 " |

| MASK0_MAP | std_logic_vector ( 107 downto 0 ) := X " 000000000000000004010222239 " |

| MASK1_MAP | std_logic_vector ( 107 downto 0 ) := X " 000000000000000000000000000 " |

| SLOT_0_CONFIG | std_logic_vector ( 7 downto 0 ) := " 00000001 " |

| SLOT_1_CONFIG | std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| IODELAY_HP_MODE | string := " ON " |

| IBUF_LPWR_MODE | string := " OFF " |

| DATA_IO_IDLE_PWRDWN | string := " ON " |

| BANK_TYPE | string := " HP_IO " |

| DATA_IO_PRIM_TYPE | string := " HP_LP " |

| CKE_ODT_AUX | string := " FALSE " |

| USER_REFRESH | string := " OFF " |

| WRLVL | string := " ON " |

| ORDERING | string := " NORM " |

| CALIB_ROW_ADD | std_logic_vector ( 15 downto 0 ) := X " 0000 " |

| CALIB_COL_ADD | std_logic_vector ( 11 downto 0 ) := X " 000 " |

| CALIB_BA_ADD | std_logic_vector ( 2 downto 0 ) := " 000 " |

| TCQ | integer := 100 |

| IODELAY_GRP | string := " IODELAY_MIG " |

| SYSCLK_TYPE | string := " DIFFERENTIAL " |

| REFCLK_TYPE | string := " NO_BUFFER " |

| SYS_RST_PORT | string := " FALSE " |

| CMD_PIPE_PLUS1 | string := " ON " |

| DRAM_TYPE | string := " DDR3 " |

| CAL_WIDTH | string := " HALF " |

| STARVE_LIMIT | integer := 2 |

| REFCLK_FREQ | real := 200 . 0 |

| DIFF_TERM_REFCLK | string := " TRUE " |

| tCK | integer := 1072 |

| nCK_PER_CLK | integer := 4 |

| DIFF_TERM_SYSCLK | string := " FALSE " |

| DEBUG_PORT | string := " OFF " |

| TEMP_MON_CONTROL | string := " EXTERNAL " |

| RST_ACT_LOW | integer := 0 |

Ports | |

| ddr3_dq | inout std_logic_vector ( DQ_WIDTH - 1 downto 0 ) |

| ddr3_dqs_p | inout std_logic_vector ( DQS_WIDTH - 1 downto 0 ) |

| ddr3_dqs_n | inout std_logic_vector ( DQS_WIDTH - 1 downto 0 ) |

| ddr3_addr | out std_logic_vector ( ROW_WIDTH - 1 downto 0 ) |

| ddr3_ba | out std_logic_vector ( BANK_WIDTH - 1 downto 0 ) |

| ddr3_ras_n | out std_logic |

| ddr3_cas_n | out std_logic |

| ddr3_we_n | out std_logic |

| ddr3_reset_n | out std_logic |

| ddr3_ck_p | out std_logic_vector ( CK_WIDTH - 1 downto 0 ) |

| ddr3_ck_n | out std_logic_vector ( CK_WIDTH - 1 downto 0 ) |

| ddr3_cke | out std_logic_vector ( CKE_WIDTH - 1 downto 0 ) |

| ddr3_dm | out std_logic_vector ( DM_WIDTH - 1 downto 0 ) |

| ddr3_odt | out std_logic_vector ( ODT_WIDTH - 1 downto 0 ) |

| sys_clk_p | in std_logic |

| sys_clk_n | in std_logic |

| clk_ref_i | in std_logic |

| app_addr | in std_logic_vector ( ADDR_WIDTH - 1 downto 0 ) |

| app_cmd | in std_logic_vector ( 2 downto 0 ) |

| app_en | in std_logic |

| app_wdf_data | in std_logic_vector ( ( nCK_PER_CLK * 2 * PAYLOAD_WIDTH ) - 1 downto 0 ) |

| app_wdf_end | in std_logic |

| app_wdf_mask | in std_logic_vector ( ( nCK_PER_CLK * 2 * PAYLOAD_WIDTH ) / 8 - 1 downto 0 ) |

| app_wdf_wren | in std_logic |

| app_rd_data | out std_logic_vector ( ( nCK_PER_CLK * 2 * PAYLOAD_WIDTH ) - 1 downto 0 ) |

| app_rd_data_end | out std_logic |

| app_rd_data_valid | out std_logic |

| app_rdy | out std_logic |

| app_wdf_rdy | out std_logic |

| app_sr_req | in std_logic |

| app_sr_active | out std_logic |

| app_ref_req | in std_logic |

| app_ref_ack | out std_logic |

| app_zq_req | in std_logic |

| app_zq_ack | out std_logic |

| ui_clk | out std_logic |

| ui_clk_sync_rst | out std_logic |

| init_calib_complete | out std_logic |

| device_temp_i | in std_logic_vector ( 11 downto 0 ) |

| sys_rst | in std_logic |

Additional Inherited Members |

Definition at line 77 of file ddr3_1_9a.vhd.

1.8.1

1.8.1