RECEIVED: May 23, 2008 ACCEPTED: August 11, 2008 PUBLISHED: September 5, 2008

# **ATLAS Muon Drift Tube Electronics**

Y. Arai,<sup>g</sup> B. Ball,<sup>j</sup> M. Beretta,<sup>d</sup> H. Boterenbrood,<sup>k</sup> G.W. Brandenburg,<sup>c\*</sup> F. Ceradini,<sup>f</sup> J.W. Chapman,<sup>j</sup> T. Dai,<sup>j</sup> C. Ferretti,<sup>j</sup> T. Fries,<sup>c</sup> J. Gregory,<sup>j</sup> J. Guimarães da Costa,<sup>c</sup> S. Harder,<sup>c</sup> E. Hazen,<sup>a</sup> J. Huth,<sup>c</sup> P.P.M. Jansweijer,<sup>k</sup> L.E. Kirsch,<sup>b</sup> A.C. König,<sup>l</sup> A. Lanza,<sup>e</sup> G. Mikenberg,<sup>m</sup> J. Oliver,<sup>c</sup> C. Posch,<sup>an</sup> R. Richter,<sup>i</sup> W. Riegler,<sup>co</sup> E. Spiriti,<sup>f</sup> F.E. Taylor,<sup>h</sup> J.C. Vermeulen,<sup>k</sup> B. Wadsworth<sup>h</sup> and T.A.M. Wijnen<sup>l</sup>

E-mail: brandenburg@physics.harvard.edu

ABSTRACT: This paper describes the electronics used for the ATLAS monitored drift tube (MDT) chambers. These chambers are the main component of the precision tracking system in the ATLAS muon spectrometer. The MDT detector system consists of 1,150 chambers containing a total of 354,000 drift tubes. It is capable of measuring the sagitta of muon tracks to an accuracy of 60  $\mu$ m, which corresponds to a momentum accuracy of about 10% at  $p_T$ = 1 TeV. The design and performance of the MDT readout electronics as well as the electronics for controlling, monitoring and powering the detector will be discussed. These electronics have been extensively tested under simulated running conditions and have undergone radiation testing certifying them for more than 10 years of LHC operation. They are now installed on the ATLAS detector and are operating during cosmic ray commissioning runs.

KEYWORDS: Electronic detector readout concepts (gas, liquid); Data acquisition circuits; Front-end electronics for detector readout; Detector control systems (detector and experiment monitoring and slow-control systems, architecture, hardware, algorithms, databases).

<sup>&</sup>lt;sup>a</sup>Boston University, Physics Department, Boston, MA, U.S.A.

<sup>&</sup>lt;sup>b</sup>Brandeis University, Department of Physics, Waltham, MA, U.S.A.

<sup>&</sup>lt;sup>c</sup>Harvard University, Laboratory for Particle Physics and Cosmology, Cambridge, MA, U.S.A.

<sup>&</sup>lt;sup>d</sup>INFN Laboratori Nazionali di Frascati, Frascati, Italy

<sup>&</sup>lt;sup>e</sup>INFN Pavia, Pavia, Italy

f INFN Roma Tre and Università Roma Tre, Dipartimento di Fisica, Roma, Italy

$<sup>^</sup>g$ KEK, High Energy Accelerator Research Organisation, Tsukuba, Japan

<sup>&</sup>lt;sup>h</sup>Massachusetts Institute of Technology, Laboratory for Nuclear Science, Cambridge, MA, U.S.A.

<sup>&</sup>lt;sup>i</sup>Max-Planck-Institut für Physik (Werner-Heisenberg-Institut), München, Germany

<sup>&</sup>lt;sup>j</sup>The University of Michigan, Department of Physics, Ann Arbor, MI, U.S.A.

<sup>&</sup>lt;sup>k</sup>Nikhef National Institute for Subatomic Physics, Amsterdam, Netherlands

<sup>&</sup>lt;sup>1</sup>Radboud University Nijmegen/Nikhef, Dept. of Exp. High Energy Physics, Nijmegen, Netherlands

$<sup>^</sup>m The\ Weizmann\ Institute\ of\ Science,\ Department\ of\ Particle\ Physics,\ Rehovot,\ Israel$

<sup>&</sup>lt;sup>n</sup>Now at the Austrian Research Center - ARC, Vienna, Austria

<sup>&</sup>lt;sup>o</sup>Now at CERN, Geneva, Switzerland

<sup>\*</sup>Corresponding author.

# Contents

| 1. | Intr | oductio                                     | on                                                        | 2  |  |  |  |  |  |  |

|----|------|---------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|--|--|

|    | 1.1  | The M                                       | IDT precision tracker                                     | 2  |  |  |  |  |  |  |

|    | 1.2  | The M                                       | IDT drift tube                                            | 4  |  |  |  |  |  |  |

|    | 1.3  | MDT readout system overview                 |                                                           |    |  |  |  |  |  |  |

|    | 1.4  | MDT                                         | readout system optimization                               | 9  |  |  |  |  |  |  |

|    | 1.5  | MDT                                         | readout system data rates                                 | 11 |  |  |  |  |  |  |

| 2. | MD   | MDT on-chamber electronics component design |                                                           |    |  |  |  |  |  |  |

|    | 2.1  | Cham                                        | ber interconnect boards                                   | 12 |  |  |  |  |  |  |

|    |      | 2.1.1                                       | Front-end interconnect board (signal hedgehog)            | 13 |  |  |  |  |  |  |

|    |      | 2.1.2                                       | On-chamber high-voltage distributor board (HV hedgehog)   | 14 |  |  |  |  |  |  |

|    | 2.2  | Front-                                      | end electronics - the mezzanine board                     | 15 |  |  |  |  |  |  |

|    |      | 2.2.1                                       | Amplifier Shaper Discriminator (MDT-ASD chip)             | 18 |  |  |  |  |  |  |

|    |      | 2.2.2                                       | Time to Digital Converter (AMT-3 chip)                    | 21 |  |  |  |  |  |  |

|    | 2.3  | On-ch                                       | namber multiplexer - Chamber Service Module (CSM)         | 25 |  |  |  |  |  |  |

|    |      | 2.3.1                                       | The passive interconnect                                  | 25 |  |  |  |  |  |  |

|    |      | 2.3.2                                       | The active CSM multiplexer                                | 26 |  |  |  |  |  |  |

|    | 2.4  | Monit                                       | oring and control - Embedded Local Monitor Board (ELMB)   | 30 |  |  |  |  |  |  |

|    | 2.5  | The ca                                      | alibration system                                         | 31 |  |  |  |  |  |  |

| 3. | On-  | chambe                                      | er electronics support services and environmental factors | 31 |  |  |  |  |  |  |

|    | 3.1  | Low-v                                       | voltage power                                             | 32 |  |  |  |  |  |  |

|    | 3.2  | High-                                       | voltage distribution                                      | 33 |  |  |  |  |  |  |

|    | 3.3  | Radiat                                      | tion tolerance of the front-end components                | 35 |  |  |  |  |  |  |

|    |      | 3.3.1                                       | Radiation levels in the MDT detector                      | 35 |  |  |  |  |  |  |

|    |      | 3.3.2                                       | Damage scenarios in electronics devices                   | 35 |  |  |  |  |  |  |

|    |      | 3.3.3                                       | Levels of test doses and test results                     | 36 |  |  |  |  |  |  |

| 4. | Off- | chamb                                       | er electronics - MDT Read Out Driver (MROD)               | 38 |  |  |  |  |  |  |

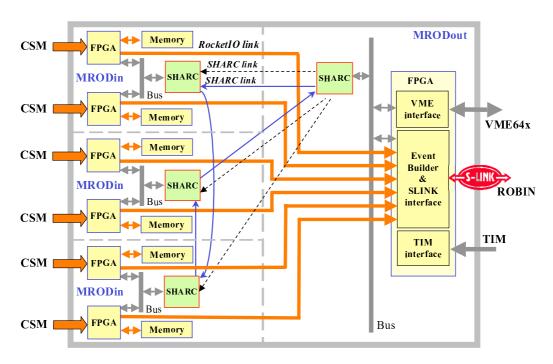

|    | 4.1  | Functi                                      | ionality                                                  | 38 |  |  |  |  |  |  |

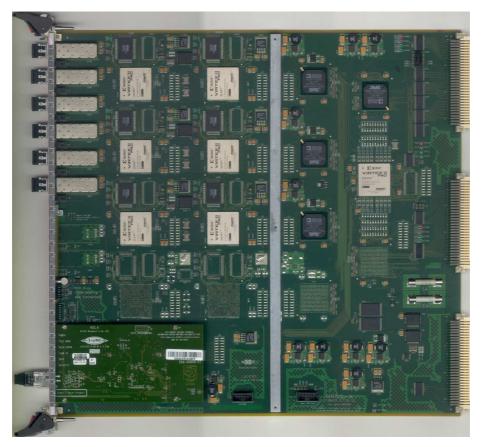

|    | 4.2  | Imple                                       | mentation                                                 | 41 |  |  |  |  |  |  |

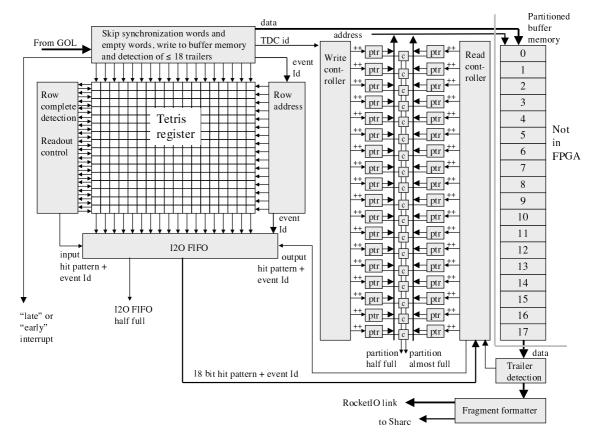

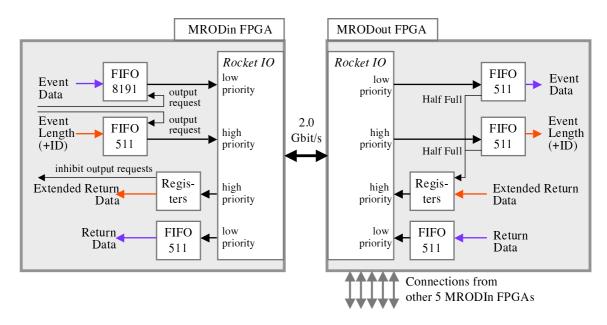

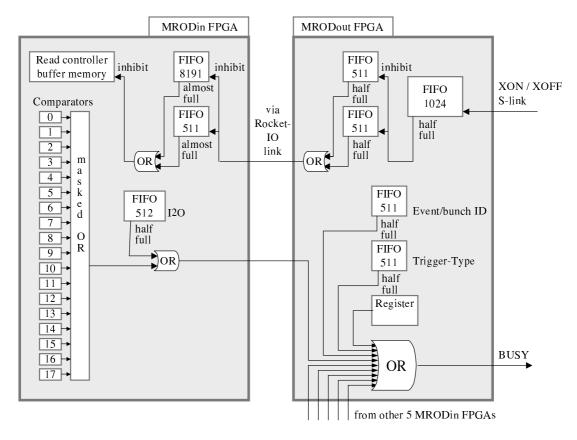

|    |      | 4.2.1                                       | The MRODin FPGA                                           | 42 |  |  |  |  |  |  |

|    |      | 4.2.2                                       | The MRODout FPGA                                          | 46 |  |  |  |  |  |  |

|    |      | 4.2.3                                       | The busy signal                                           | 47 |  |  |  |  |  |  |

|    |      | 4.2.4                                       | Configuration of the FPGAs                                | 48 |  |  |  |  |  |  |

|    |      | 4.2.5                                       | Software environment                                      | 49 |  |  |  |  |  |  |

|    |      | 4.2.6                                       | Monitoring                                                | 49 |  |  |  |  |  |  |

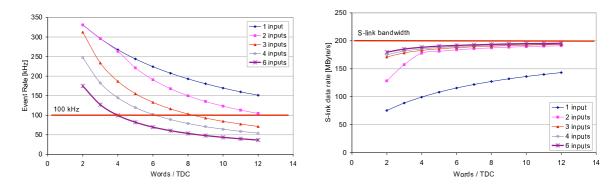

|    | 4.3  | Throu                                       | ghput tests                                               | 50 |  |  |  |  |  |  |

| 5. | Syst | em test                                     | ts                                                        | 50 |  |  |  |  |  |  |

6. Conclusions 53

# A. MDT chamber specifications

53

## 1. Introduction

The monitored drift tube (MDT) chambers are the main component of the precision tracking system in the ATLAS muon spectrometer [1]. The precisely manufactured MDT chambers are carefully monitored within the ATLAS detector for their position, internal deformations, and environmental conditions like temperature and magnetic field. Due to the combination of mechanical accuracy of each chamber and external position monitoring ("alignment"), the MDT system achieves a sagitta accuracy of 60  $\mu$ m, corresponding to a momentum resolution of about 10% at p<sub>T</sub>= 1 TeV/c. The 1,150 MDT chambers are made from 354,000 tubes and cover an area of 5,500 m<sup>2</sup>.

The main task of the readout electronics is to preserve the inherent measurement accuracy of the tubes ( $80~\mu m$ ) and to cope with the high hit rates expected at full LHC luminosity (up to 300~kHz per tube). In order to obtain the required tracking accuracy the front-end electronics have been implemented with a low-impedance, low-noise amplifier-shaper-discriminator (ASD) together with a high resolution TDC. To process the high data rates, the system architecture is based on fine segmentation of the readout (24~tubes per TDC), fast local processors, large storage capacities at each level of data processing and high-speed data links. The front-end electronics have also been designed to survive in a high radiation environment and have undergone testing certifying them for more than 10~years of LHC operation. In addition to reading out the MDT chambers, electronics are necessary to control the readout system, to monitor the chamber environment and running conditions, and to supply the necessary low and high voltage power.

The organization of this paper is as follows. In the remainder of this section an overview of the MDT system is presented, which includes a summary of both the chamber mechanical design and the associated readout electronics. Section 2 contains a detailed discussion of the design of the onchamber electronics for reading out and monitoring the system, while section 3 covers the support services for their operation and the environmental factors that affect them. Section 4 describes the design and implementation of the off-chamber readout electronics. The final two sections discuss the testing of the system with cosmic rays and muon beams, and present some conclusions. An appendix is attached which tabulates the parameters of the individual MDT chambers for reference purposes. Electronics related to chamber alignment are not covered in this paper - see references [2] and [3] for the barrel and end-cap alignment systems respectively.

### 1.1 The MDT precision tracker

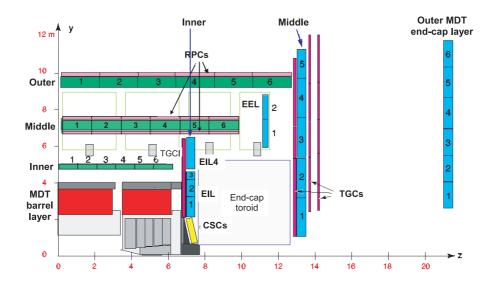

The muon spectrometer of the ATLAS detector is illustrated in figure 1. It is designed to detect charged particles exiting the barrel and end-cap calorimeters and to measure their momenta at polar angles greater than 7.7° corresponding to pseudo-rapidity  $|\eta| \le 2.7$ .

The primary momentum measurement in the muon system is provided by monitored drift tube chambers (MDTs) which consist of pressurized drift tubes with a diameter of 30 mm, operating

**Figure 1.** Cross-section of the muon system in a plane containing the beam axis. MDT chambers in the barrel (green) and in the end-cap (blue) are arranged in three layers around the hadronic calorimeters (red and grey). In the first layer of the end-cap, cathode strip chambers (yellow) are used near the beam-pipe instead of MDTs to cope with the expected high track densities at  $\eta \ge 2.4$ . The chambers marked RPCs and TGCs are the trigger chambers in the barrel and end-cap regions.

with Ar/CO<sub>2</sub> gas (93/7) at 3 bar. In the very forward region ( $2 < |\eta| < 2.7$ ) of the innermost tracking layer cathode strip chambers (CSCs) are used due to their higher rate capability and time resolution [4]. Input to the Level-1 muon trigger [5], which selects muons pointing to the interaction region with transverse momenta above a programmable threshold, is provided by fast tracking detectors. These detectors are resistive plate chambers (RPCs) in the barrel region and thin gap chambers (TGCs) in the end-cap region [4]. Their time resolution guarantees the identification of the interaction bunch crossing, and their readout segmentation in the direction along the MDT wires measures the  $\phi$  coordinate with a resolution of 1 cm.

The MDT chambers are arranged in three layers along the trajectory of the track, which allows a determination of the momentum from the sagitta of the track's curvature in the magnetic field. In the barrel part of the detector the three layers form coaxial cylinders, in the end-cap part they form large circular disks centered at the beam axis. In the inner MDT layer each chamber consists of eight tube layers which are segmented in two "multi-layers" of four tube layers each. In the middle and outer MDT layers the chambers consist of six tube layers divided into multi-layers of three tube layers. The multi-layers in a chamber are separated by a spacer for structural reasons as well as to permit a crude momentum measurement for low momentum tracks and the construction of a track segment for high momentum tracks. The distance between the multi-layers varies between 6 and 121 mm in the inner layer and between 170 and 317 mm in the middle and outer layers.

MDT chambers are rectangular in the barrel and trapezoidal in the end-cap, being built in various dimensions to optimize solid angle coverage. Apart from the length, all MDT tubes are identical. In the final implementation, the MDT system will consist of 656 chambers in the barrel and 494 chambers in the end-caps. A detailed list of chamber types and dimensions is given in the

appendix in table 12 for the barrel and in table 13 for the end-cap chambers. Construction parameters of the different MDT chamber types and their locations in the detector are presented in [6].

With an average tube resolution of 80  $\mu$ m, a chamber resolution of 40  $\mu$ m and 35  $\mu$ m is achieved for 6 and 8 layer chambers, respectively. A detailed descriptions of the muon system is given in reference [4].

#### 1.2 The MDT drift tube

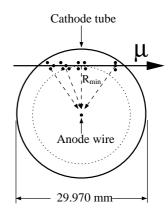

Figure 2 shows the cross-section of a MDT tube. The wall thickness is 0.4 mm and the inner radius is 14.58 mm ( $R_{max}$ ). For each track the electrons from the primary ionisation clusters drift to the central wire along radial lines, the corresponding drift lengths ranging from  $R_{min}$  to  $R_{max}$ .

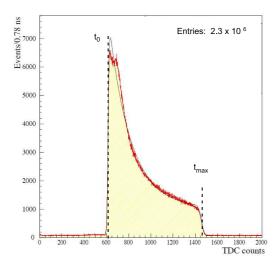

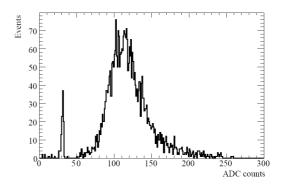

In the Ar/CO<sub>2</sub> gas the drift velocity shows a strong dependence on the radius, i.e. 10  $\mu$ m/ns close to the wall, 26  $\mu$ m/ns at r = 7,25 mm and 52  $\mu$ m/ns close to the wire. The exact shape of the radius-to-drift time relation (r-t relation) depends on parameters like temperature, pressure, magnetic field and total hit rate in the tube; the latter being due to field distortions caused by the positive ions. Figure 42 in section 5 displays an example of the drift-time spectrum. In order to make optimal use of the inherent spatial resolution of the MDT tube, the r-t relation must be known with high accuracy, which is achieved by continuous

**Figure 2.** MDT tube cross-section with ionisation clusters distributed along a track.

calibration with tracks in the ATLAS experiment. The operating parameters of the MDT tubes are given in table 1.

The main sources of the measurement error in the MDTs are diffusion and the uneven distribution of location and ionisation density of the primary clusters along the track. The electrons arriving earliest at the wire will in general come from a point along the track which is slightly displaced with respect to  $R_{min}$ , leading to an increased travel time to the wire. The operation of the drift tubes at a pressure of three atmospheres reduces diffusion as well as the fluctuation of both ionisation and cluster location. A detailed discussion of the various physics contributions to the

**Table 1.** Main MDT chamber parameters.

| Parameter              | Design value              |

|------------------------|---------------------------|

| Wire diameter          | 50 μm                     |

| Gas mixture            | Ar/CO <sub>2</sub> (93/7) |

| Gas pressure           | 3 bar (absolute)          |

| Gas gain               | $2 \times 10^4$           |

| Wire potential         | 3080 V                    |

| Average drift velocity | $\sim$ 20.7 $\mu$ m/ns    |

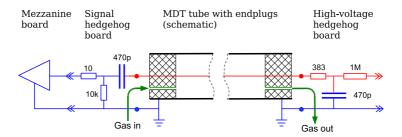

**Figure 3.** Main service connections to a MDT tube. At the high-voltage side the wire is terminated with the equivalent transmission line impedance of the tube (383  $\Omega$ ) to avoid reflections. All contacts (round dots) between the chamber and the hedgehog boards are gold plated to ensure a long-term connectivity.

resolution is given in [7]. Though the work described in reference [7] was done for a different gas, the general results are also applicable to the Ar/CO<sub>2</sub> gas [8].

The contribution from *electronics* to the drift time resolution is mainly due to two parameters:

- The rise time of the amplifier combined with the discriminator threshold, which determines the time needed to trigger the TDC. With the performance parameters of the electronics discussed below (see section 1.4) this contributes an average error of 20-25 μm. This error can be further reduced if the charge in the leading edge is measured and a corresponding "slewing" correction is applied (see section 1.4).

- The least significant bit (LSB) error of the TDC, which is 25 ns/32 = 0.78 ns, corresponding to an RMS-error of 0.23 ns. This contributes an average error of 20  $\mu$ m to the measurement of  $R_{min}$ .

In an MDT tube each track creates a sequence of pulses, the duration of which corresponds to the time difference in drifting from  $R_{min}$  and  $R_{max}$ . While only the electrons arriving earliest at the wire, namely those coming from the cluster created nearest to the anode wire (approximately from  $R_{min}$ ), are used for the determination of the track coordinate, the subsequent ones will create additional threshold crossings, inflating the data volume to be read out. Therefore, the electronics have the capability to disable the discriminator for a certain time after the initial threshold crossing by means of a programmable dead-time. A detailed discussion of the time structure of the pulses is given in [9].

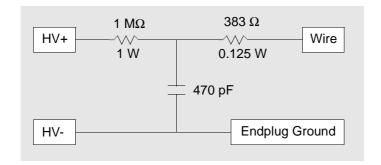

A schematic drawing of the MDT drift tube connections to the electrical services is shown in figure 3. At the right end is the high-voltage "hedgehog" board (section 2.1.2) where a 383  $\Omega$  resistor terminates the tube with its characteristic transmission line impedance and which also contains decoupling capacitors and protection components. The termination resistor suppresses signal reflection at the open end of the wire, however, it is also a significant source of thermal noise (see section 1.4). At the left end the signal hedgehog board (section 2.1.1) connects the tube to the "mezzanine" board (section 2.2) which contains the active readout electronics.

An aluminum Faraday cage completely surrounds the electronics at both ends of the chamber to provide shielding from external noise sources. The metallic surface of each tube is grounded at both ends to the hedgehog boards and to the bottom plates of the Faraday cages, which are in turn

**Figure 4.** A photograph of the readout end of an end-cap MDT chamber where the assembly has been staged in sections to illustrate the tube ends with gas tubelets visible (upper center), one hedgehog board attached to the tube ends (upper right), one mezzanine board plugged through the inner Faraday cover (lower left), and a completely enclosed mezzanine board (lower right). In the center is the "chamber service module" (CSM) without its protective cover, and the red box to its left contains an "embedded local monitoring board" (ELMB).

connected to the aluminum support structure of the chamber. The Faraday cages have undergone a chemical surface treatment (chromatisation) to assure a conductive, unalterable surface.

A photograph of the readout end of an MDT chamber showing the location of the electronics components is shown in figure 4. Individual tube signals and grounds are carried via board-to-board connectors from the hedgehog board to the mezzanine board. Ground planes have been added on the top and bottom layers of the signal hedgehog board to shield the long signal traces on the board from the digital noise on the mezzanine boards. The two boards have also been separated by an aluminum inner wall of the Faraday cage (see figure 4), the so called "box-on-box" design. With this design excellent noise immunity has been achieved.

### 1.3 MDT readout system overview

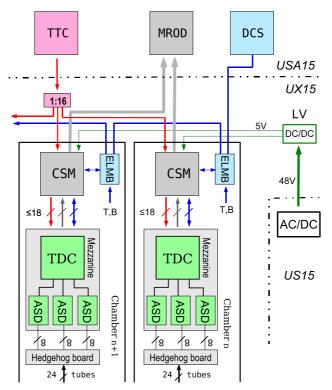

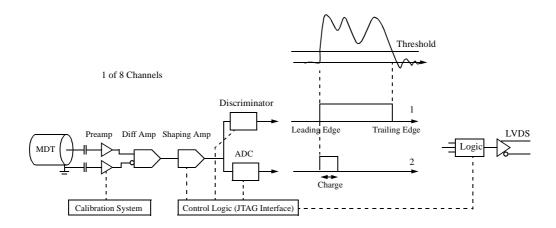

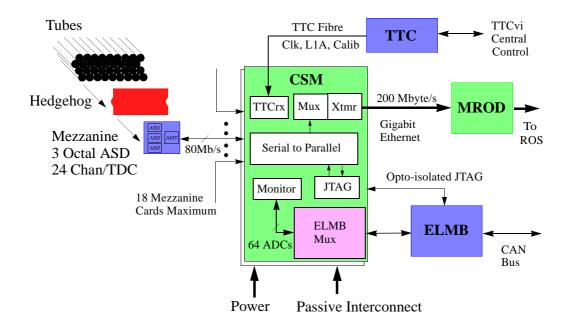

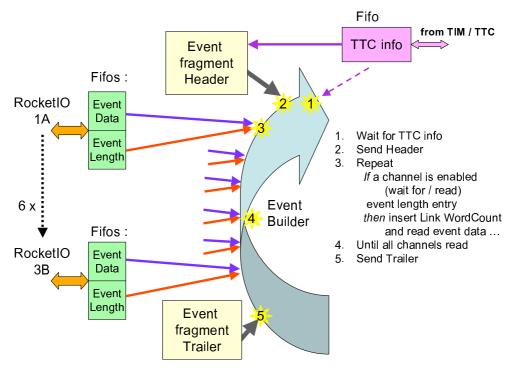

The architecture of the MDT readout is shown in figure 5. In the first stage, the raw signals from 24 tubes are routed via the signal hedgehog boards to the mezzanine boards where they are amplified, discriminated, and digitized. On the mezzanine board the signals from eight tubes are first processed by one of three custom-designed monolithic Amplifier/Shaper/Discriminator (ASD) chips. The binary differential signals output by the ASDs are then routed to the Time-to-Digital Converter (TDC) chip, where the arrival times of leading and trailing edges are stored in a buffer memory of 256 words. Each time measurement is paired together with an identifier of the corresponding tube. The time is measured in units of the Timing, Trigger and Control (TTC) clock of 40.08 MHz [10], which is the bunch crossing (BC) frequency of the LHC machine. There are 4096 bunches in a ma-

**Figure 5.** Schematic diagram of the MDT readout electronics. Each CSM serves up to 18 mezzanine boards depending on chamber size, each MROD up to 6 CSMs.

chine cycle, so the BC or "coarse time" is described by a 12 bit word. In the TDC the BC interval of 24.95 ns is subdivided by 32 via a Delay Locked Loop (DLL) resulting in a "fine time" period of 0.78 ns. This leads to an RMS timing error of 0.23 ns in measuring the arrival times.

An additional programmable feature of the ASD is the measurement of the pulse height of the signal, which allows for the monitoring of the gas gain as well as for pulse height dependent "slewing" corrections to the timing. The pulse height is encoded as the time interval between the leading and trailing edge of the ASD output pulse, with an output pulse width of 150 ns corresponding to the maximum input pulse height to be recorded. With this feature enabled the trailing edge of the ASD output pulse does not depend on the discriminator status and the discriminator is disabled until after the pulse height encoding has safely elapsed. Additional discriminator dead-time is also programmable and can be increased up to 750 ns in order to mask multiple hits from the same track. <sup>1</sup>

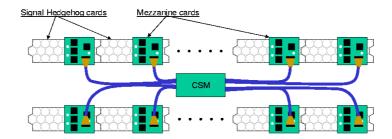

The mezzanine board containing the TDC chip plus three ASD chips, and serving 24 tubes, is the basic readout element of the MDT chambers. MDT chambers contain up to 18 mezzanine boards which are controlled by a local processor, the Chamber Service Module (CSM), as shown in figure 5. The interconnection scheme between CSMs and mezzanine boards is illustrated in figure 6. High-density 40 pin twisted pair cables are used to transmit control signals as well as supply power.

$<sup>^{1}</sup>$ For tracks passing near the wire there are ionisation clusters extending from the minimum to the maximum times corresponding to  $R_{min}$  and  $R_{max}$  respectively, and as a result the shaper circuit has to integrate a large amount of charge. When the shaper is finally "released" the signal may overshoot the baseline outside the dead time window resulting in increased noise at times greater than the maximum allowable.

**Figure 6.** The CSM collects data from up to 18 mezzanine boards which serve 24 MDT tubes each. Data are transmitted via high-density twisted pair cables from the mezzanine boards to the CSM.

JTAG [11] information is distributed by the detector control system (DCS) through a serial bus system called the CANbus [12], using the CANopen protocol [13]. Each chamber contains a CANbus node located on the Embedded Local Monitor Board (ELMB) [14] The ELMB executes the JTAG operations, loads configuration code into the CSM, and monitors temperature sensors and supply voltages on the CSM and mezzanine boards, as well as temperature and magnetic field values from sensors distributed over the chamber. The ELMB interfaces to the CSM via opto-couplers, such that there is no DC connection between the CSM/chamber ground and the CANbus wires.

Programming of the CSM and of the ASD and TDC chips on each mezzanine board is done over JTAG, allowing for a string of 72 bits for the CSM, of 160 bits per three ASD chips and of 180 bits per TDC chip. In this way, many parameters and functions can be controlled, including the setting of the discriminator threshold and dead-time, triggering of test pulses for calibration, or deactivation of noisy channels.

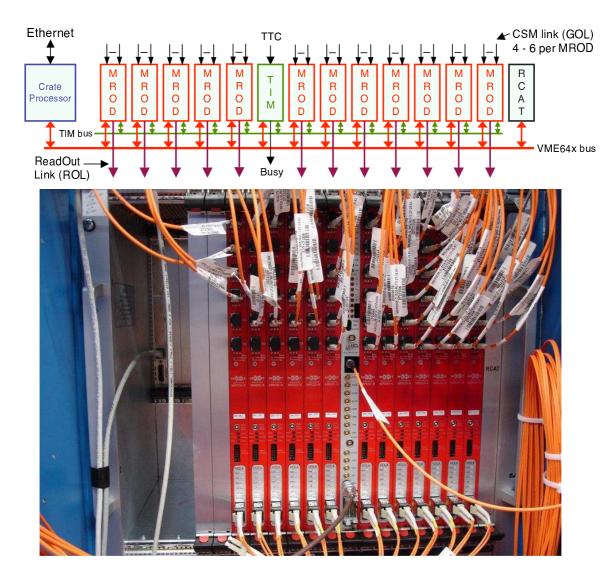

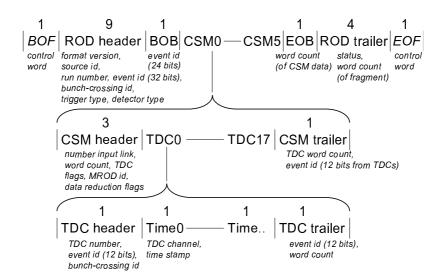

The CSM communicates with the off-chamber electronics via two fibers, one coming from the TTC distribution box and the other going to the MDT Readout Driver (MROD) [15]. During normal data taking, the CSM broadcasts the TTC control and trigger signals to the TDCs and collects the data coming from the TDCs in response to all the Level-1 triggers. Subsequently, the data are formatted, stored in a de-randomizing buffer, and sent via an optical link to the MROD in the USA15 service cavern. The MROD is a VME module, serving up to six CSMs. Its main task is to assemble the data associated with each event for rapid transfer to the Readout Buffer (ROB) [16] where data are stored until the event has been either accepted or rejected by the Level-2 trigger. Table 2 summarizes the modularity of the readout system.

**Table 2.** Modularity of the MDT readout electronics. The difference between the number of chambers and CSMs in the barrel is due to some CSMs serving a pair of chambers. The allocation of MRODs to the barrel or end-cap is approximate, some MRODs serving CSMs from both regions.

| Region      | Tubes  | ASDs  | Mezz. boards | CSMs | Chambers | MRODs |

|-------------|--------|-------|--------------|------|----------|-------|

| Barrel      | 191568 | 24114 | 8038         | 624  | 656      | 100   |

| Two endcaps | 162816 | 20352 | 6784         | 494  | 494      | 104   |

| Total       | 354384 | 44466 | 14822        | 1118 | 1150     | 204   |

**Table 3.** Power consumption of components, a mezzanine board, an "average" MDT, a "maximum" MDT (with 18 mezzanine boards) and the overall system. An average MDT has a calculated 308 tubes, served by approximately 13 mezzanine boards. The current drawn by an average and a maximum MDT is 6.3 and 8.3 A respectively. The average consumption per tube is 82 mW excluding, and 93 mW including the cable loss.

|                                           | Component |       | Mezz. | MDT  | Chamber | System    |

|-------------------------------------------|-----------|-------|-------|------|---------|-----------|

|                                           |           |       |       | avg. | тах.    | 1150 ch's |

|                                           | mW        | count | mW    | W    | W       | kW        |

| ASD                                       | 300       | 3     | 900   |      |         |           |

| AMT                                       |           | 1     | 360   |      |         |           |

| Drivers / Receivers                       |           | 1     | 90    |      |         |           |

| Mezzanine board @ 3.3 V                   |           |       | 1350  |      |         |           |

| Voltage regulator 4 V $\Rightarrow$ 3.3 V |           |       | 280   |      |         |           |

| Mezzanine board @ 4 V                     |           |       | 1630  |      |         |           |

| MDT, excluding CSM                        |           |       |       | 21.2 | 29.3    |           |

| CSM (1 A @ 4 V)                           |           |       |       | 4.0  | 4.0     |           |

| Complete MDT at 4 V                       |           |       |       | 25.2 | 33.3    |           |

| Total MDT (excl. supply cables)           |           |       |       |      |         | 29        |

| Supply cable loss ( $\sim 15\%$ )         |           |       |       |      |         | 4         |

| Total MDT (incl. supply cables)           |           |       |       |      |         | 33        |

An important feature of the MROD is its processing power that allows it to monitor the incoming data. The data streams received from the CSMs can be sampled for tube and chamber occupancies and their deviations from nominal values, possibly pointing to a malfunction. As the MRODs see the full Level-1 event rate, they can accumulate significant statistics in a short time, allowing for an early recognition of errors. Depending on average event size and Level-1 rate, a variable fraction of the events will be monitored in order to not slow down data transfer to the ROBs, which has priority.

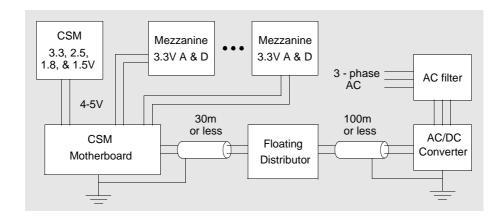

Power for the on-chamber readout electronics is routed via a shielded cable from a single DC source to the CSM and is then distributed separately to the analog and digital circuitry on the mezzanine boards. The source voltage is adjusted to deliver approximately 4 V at the CSM. Each mezzanine board draws about 270 mA for the analog part and 140 mA for the digital part at about 4 V, which is regulated to 3.3 V by on-board regulators. Thus the total power consumption of a mezzanine board is 1.6 W, including the power used by the voltage regulators. The CSM, including its regulators, consumes about 4 W, a large chamber with mezzanine boards for 432 tubes consumes 33 W, and the entire MDT system consumes 37 kW. A breakdown of the power consumption of the MDT readout electronics is given in table 3.

### 1.4 MDT readout system optimization

Extensive test-beam measurements and simulations have been performed in order to study the spatial resolution of the MDT system under different operating conditions and to optimize the

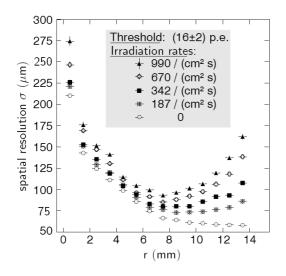

**Figure 7.** Spatial resolution of a drift tube as a function of the drift distance r at various levels of  $\gamma$ -irradiation with a threshold of 16 photoelectrons (p.e.).

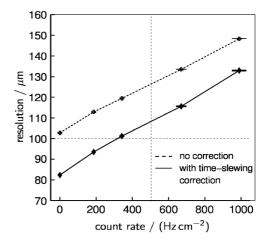

**Figure 8.** Effect of the time-slewing corrections on the average spatial resolution of a the drift tubes. The maximum rate expected for the MDTs is  $\leq 150$  Hz/cm<sup>2</sup>.

parameters for the front-end electronics [17, 18]. As an example, figure 7 shows the resolution as a function of the drift distance at different background rates ([9, 19–21]). Background hits, due to converted neutrons and  $\gamma$ 's, lead to space charge in the drift gas and, consequently, to drift field fluctuations which reduce the resolution. This effect, increasing with the distance from the wire, is clearly visible in the figure. The tube signals in the Ar/CO<sub>2</sub> gas and the electronics response have been simulated with the GARFIELD program and are in good agreement with the measured resolution, illustrating that the performance of the MDT system is quite well understood.

The baseline choice for the gas gain of the MDT tubes is  $2 \times 10^4$ . The minimum practical discriminator threshold is five times the noise level, which in the MDTs is dominated by termination resistor thermal noise. Using pre-amplifier peaking times of less than 5 ns does not improve the MDT resolution since the signal-to-noise ratio rapidly becomes worse for such short peaking times.

If the MDTs were operated at a very high gas gain ( $> 10^5$ ), the signal-to-noise ratio would be high, permitting operation at a wide range of discriminator thresholds. In that case the resolution would be best for very fast pre-amplifiers (peaking times of 3-4 ns) and very low thresholds (3-5 electrons). However, owing to the high background rates in the spectrometer, the possible degradation of the chamber performance (ageing) caused by large amounts of charge deposited on the anode wire would be a serious problem. The ageing effects are therefore minimized by operating the chamber at the lowest possible gas gain which is still compatible with the electronic noise and spatial resolution requirements.

Another disadvantage of using a fast pre-amplifier is the sensitivity to individual ionisation clusters which causes multiple threshold crossings per signal and therefore a significant increase in the hit rate. Therefore a choice of a rise time of about 15 ns is the best compromise in terms of resolution, noise sensitivity, overall stability and choice of ASIC technology.

Taking into account only the termination resistor noise, the five times noise level corresponds

to 17 primary electrons for the baseline gas gain. A detailed analysis of the current pre-amplifier design showed that trace capacitances on the board and other parasitic capacitances increase this threshold level to 22–25 electrons [22].

The change in resolution for different thresholds and peaking times is primarily due to time slewing corresponding to different signal rise times from charge fluctuations in the leading edge. By measuring the charge in the leading edge with a short gate ADC (gate time less than twice the peaking time), a correction for the time slewing can be made to improve the resolution [17]. Figure 8 shows the gain in resolution obtained by the slewing correction with little dependence on the background rate. At the maximum expected rate of 150 Hz/cm<sup>2</sup> a resolution of 90 and 110  $\mu$ m is obtained with and without the correction. To avoid further loss in resolution caused by charge fluctuation, the discriminator time walk should be less than 500 ps (corresponding to an average position error of about 10  $\mu$ m) for the entire signal input range.

To minimize the number of threshold crossings per track the discriminator has a programmable amount of hysteresis. For a gas gain of  $2 \times 10^4$  and a threshold of 24 electrons including some hysteresis, 1-2 threshold crossings per signal is typical for the standard tail cancellation with a two stage pole/zero filter used. In order to ignore unwanted secondary hits, the ASD can be operated in a programmable dead-time mode, suppressing trailing hits for a preset interval [23].

In case of a Level-1 trigger all accepted hits within the maximum drift time window are read out. If the pattern recognition algorithm finds a tube to be inefficient it is useful to know the reason for the inefficiency. Reading out the hits within a window preceding the actual drift time window allows one to determine whether an earlier hit (possibly caused by a  $\gamma$ -conversion) could have obscured the hit from the muon track. To minimize bandwidth requirements a single bit is set by the TDC to flag as pile-up the occurrence of any hits prior to the digitization window.

The requirements on bandwidth, buffer memory in the TDC, and serial link speed are mainly determined by the background hit rates. According to detector simulations the maximum count rate per tube in the MDT system is 300 kHz (including a safety factor of five for the uncertainty in the background simulation). The options implemented in the ASD-TDC design for various quantities of interest (leading and trailing edges, integrated signal leading edge and multi-hit information) are discussed in the following sections.

# 1.5 MDT readout system data rates

The flow of data through the front-end is subject to the rate of hits in the MDT tubes and varies widely over the span of chambers. Estimates of the rates (with a safety factor of five) for chambers at small angles to the beam line and for the inner layers, approach saturation of the TDC processing capacity at  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> luminosity. The majority of the hits are not from muon tracks but from photon and neutron induced ionisation. The TDC is designed to remove old hits from its buffer when average tube rates exceed 300 kHz (see section 2.2.2).

Table 4 displays the data flow rates from the TDC through the CSM. The ATLAS wide maximum trigger rate, 100 kHz, is used in the rate calculation along with an 800 ns TDC "search window" for each trigger. The maximum rate on the TDC-CSM link is 80 Mbit/s. Four different tube hit rates chosen for illustration. The 0 kHz value is included to show the bandwidth occupied by synchronization words (called headers and trailers) and mask words that flag prior hits. Each

**Table 4.** The relationship between tube hit rates in kHz and the link occupancy at low, medium and high hit rates of the MDT tubes. A hit rate of 0 is included to illustrate the bandwidth occupied by TDC headers, trailers, and mask words.

| Ungated hit rate per tube [kHz]             | $\Longrightarrow$ | 0     | 75    | 150   | 300   |

|---------------------------------------------|-------------------|-------|-------|-------|-------|

| Gated tube hit rate                         | [kHz]             | 0     | 6     | 12    | 24    |

| Gated TDC hit rate                          | [kHz]             | 0     | 144   | 288   | 576   |

| Gated TDC word rate                         | [kHz]             | 300   | 588   | 876   | 1452  |

| Gated TDC bit rate                          | [Mbits/s]         | 10.8  | 21.2  | 31.5  | 52.3  |

| Fraction of TDC $\Longrightarrow$ CSM link  | percentage        | 13.5% | 26.5% | 39.4% | 65.3% |

| Per 18 mezz board chamber                   | [Mbits/s]         | 172.8 | 338.7 | 504.6 | 836.4 |

| Fraction of CSM $\Longrightarrow$ MROD link | percentage        | 12.6% | 24.7% | 36.8% | 61.0% |

TDC sends one each of these three words for each trigger. The first row of table 4 represents ungated hit rates. The remaining rows represent data selected for output by the trigger and gate width. The processing bandwidth of the CSM is designed to pass all incoming data. The removal of hits at high rates is left exclusively to the TDC where a flag is provided with each data word to indicate when prior hits were lost.

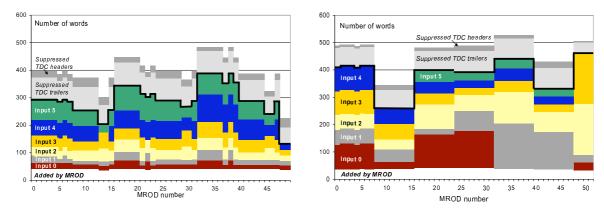

Data flows from the CSM to the MROD over a 1.6 Gigabit/s link and consists of TDC output from up to 18 mezzanine boards, two optical synchronization words and one readout cycle synchronization word (see section 2.3.2). The available bandwidth for chamber data is thus reduced by an 18/21 ratio to 1.37 Gigabit/s. The rate of data transmission from CSM to MROD exceeds the sum of the total input rate from 18 mezzanine boards and yields a slightly lower percentage occupation in each case in the table. It should also be noted that the chambers in the regions with the highest rates have 16 or fewer mezzanine boards. See figure 34 for a more detailed evaluation of the expected data rates into the MRODs.

Flow control within each MROD is provided by a ROD busy output, and a logical OR of all such busy signals inhibits triggers. The ROD busy design is an ATLAS wide feature and not exclusive to the muon system.

# 2. MDT on-chamber electronics component design

The on-chamber electronics components consisting of the hedgehog boards, the mezzanine boards, the chamber service module (CSM), and the local monitor board (ELMB), are described in detail in this section.

## 2.1 Chamber interconnect boards

At both ends of an MDT chamber there are interconnect ("hedgehog") boards which passively terminate the drift tube wires with capacitors and resistors. At one end the signal hedgehog boards couple the tubes with the front-end readout electronics (section 2.2), while at the other end the high-voltage (HV) hedgehog boards connect the tubes to the high-voltage distribution system (sec-

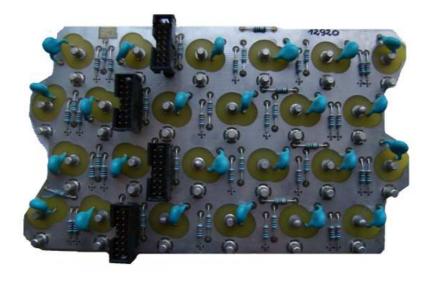

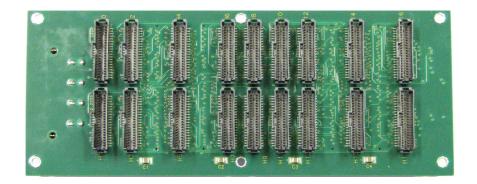

Figure 9. A signal hedgehog board for 4 tube layer chambers.

tion 3.1). Each hedgehog board services 24 tubes. At each end of the chamber the hedgehog boards are enclosed in Faraday cages to shield the tube connections.

#### 2.1.1 Front-end interconnect board (signal hedgehog)

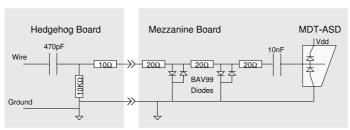

An example of a signal hedgehog board is shown in figure 9. For each tube this board contains both signal and ground receptacles together with a HV-decoupling capacitor and two resistors that form a protection network (see figure 14 in section 2.2). A mezzanine board plugs directly onto the pin headers of the hedgehog board.

The signal hedgehog is a four-layer printed circuit board with the signal traces routed on the two internal layers. The two external layers are ground planes covering as much surface area as possible taking in consideration the necessary clearance around the HV receptacles. The ground planes are required to shield the signal traces from HF noise generated by the TDC clock on the mezzanine board.

There are four different types of signal hedgehogs, two of each for the 3-layer and 4-layer MDT chambers respectively. For each kind of chamber the two types geometrically fit the shapes of the two multi-layers. The 3-layer boards have 8 channels (tubes) per layer and the 4-layer boards have 6 channels per layer, both totaling 24 channels. The board shown in figure 9 is for a 4-layer chamber.

The HV-decoupling capacitor is a 470 pF, 6.3 kV ceramic capacitor produced by Murata. The same type is used in the HV hedgehogs. It is placed in series with the signal path, so the signal quality could possibly be degraded by its performance. For this reason, its stability was extensively tested under different HV, temperature and humidity conditions. Its mean failure rate has been measured to be 0.0004% per unit for every 1000 hours of operation [24].

Each of the 24 MDT tubes serviced by a signal hedgehog board is connected to a unique TDC channel on the attached mezzanine board, and the TDC channel number is the identifier for that

**Table 5.** The mapping between the MDT tube location and the TDC channel number for the four signal hedgehog board types. The orientation and placement of the different hedgehog types depends on chamber type and location within the detector [25], [26].

| Type          | Row | TDC Channel # for Tubes in Layer |

|---------------|-----|----------------------------------|

| I (3-layer)   | 1   | 1, 3, 5, 7, 6, 0, 4, 2           |

| "             | 2   | 9, 11, 13, 15, 14, 8, 12, 10     |

| "             | 3   | 17, 19, 21, 23, 22, 16, 20, 18   |

| II (3-layer)  | 1   | 1, 3, 5, 7, 6, 4, 2, 0           |

| "             | 2   | 9, 11, 13, 15, 14, 12, 10, 8     |

| "             | 3   | 17, 19, 21, 23, 22, 20, 18, 16   |

| III (4-layer) | 1   | 5, 3, 4, 2, 0, 1                 |

| "             | 2   | 11, 9, 10, 8, 6, 7               |

| "             | 3   | 17, 15, 16, 14, 12, 13           |

| "             | 4   | 23, 21, 22, 20, 18, 19           |

| IV (4-layer)  | 1   | 3, 1, 5, 0, 2, 4                 |

| "             | 2   | 9, 7, 11, 6, 8, 10               |

| "             | 3   | 15, 13, 17, 12, 14, 16           |

| "             | 4   | 19, 21, 23, 18, 20, 22           |

tube in the output data stream. The mapping between tube location and TDC number is different for each hedgehog type and is given in table 5.

The signal hedgehog boards are conformally coated with Dow Corning R4-3117 RTV. This eliminates leakage current between the traces as long as the relative humidity is less than approximately 50%. The insulation properties of this product were shown to be adequate after both neutron and gamma radiation.

#### 2.1.2 On-chamber high-voltage distributor board (HV hedgehog)

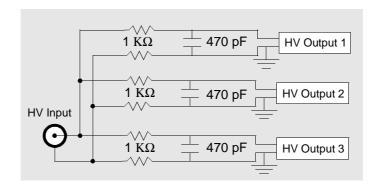

The distribution of high-voltage to the MDT tubes is done by the HV hedgehog board, which is mechanically interfaced with the tubes using the same receptacles as on the signal hedgehogs. The schematic of a single channel of this board is shown in figure 10. The combination of the 1 M $\Omega$  resistor and 470 pF capacitor filters the high-frequency noise (> 500 Hz) on the high-voltage line. In the case of a wire short the maximum HV supply current set on the distributors, which cannot be greater than 0.7 mA, will flow through the 1 M $\Omega$  resistor for a period of 0.1 seconds, after which time the HV will be shut off. The capacitor is the same type as described in the signal hedgehog section. The final component is the 383  $\Omega$  resistor, which is in series with the tube matching its impedance.

As with the signal hedgehogs, there are 24 channels on each board, distributed in 3 rows of 8 channels each or in 4 rows of 6 channels each for the 3-layer and 4-layer chambers respectively. The layout is designed on two layers, without shielding layers, taking in account the minimum clearance of 3 mm between high-voltage and ground. The irregular design of some chamber Faraday cages plus the need for special HV hedgehogs that connect to the external HV source leads to a much

Figure 10. Schematic of one HV hedgehog channel.

Figure 11. A 3-layer barrel HV hedgehog board.

larger number of board designs than in the case of the signal hedgehogs. The total number of HV hedgehog types is 28: 22 for the barrel and 6 for the end-cap. A typical 3-layer HV hedgehog for the barrel MDTs is shown in figure 11.

The high-voltage lines coming from the external HV splitter box are connected to only one HV hedgehog for each multi-layer. This particular board has additional connectors installed: for the barrel chambers they are AMP two-position connectors, separated for high-voltage and ground, and for the end-cap they are Molex five-position connectors, with high-voltage and ground contacts on the same connector. In order to pass the high-voltage line through the full multi-layer, each high-voltage line on the hedgehogs is daisy-chained from board to board. In the barrel this is done using gilded jumpers. The end-cap HV hedgehogs are stepped due to the trapezoidal geometry of the chambers, and in this case chaining is done by means of wire jumpers connecting Molex multi-pin connectors on adjacent boards. Because of the high voltages present on the hedgehog boards, they are expected to operate in a relative humidity less than approximately 50%.

## 2.2 Front-end electronics - the mezzanine board

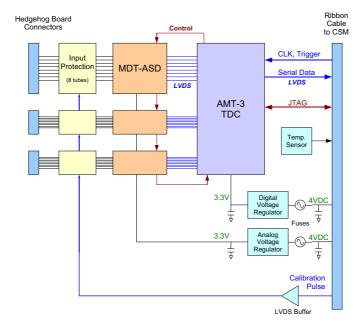

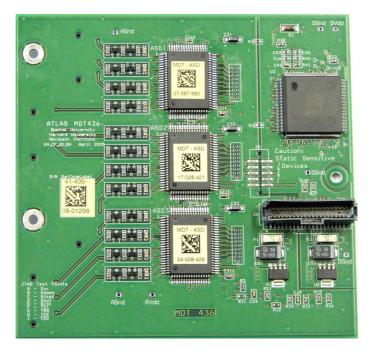

The mezzanine board carries the active electronics for 24 MDT channels and comes in different configurations for chambers with 3 and 4 tube layers. A block diagram of the mezzanine board is shown in figure 12 and a picture of a 3 tube layer board is shown in figure 13. Three MDT-ASD chips, one TDC chip, two voltage regulators, LVDS-drivers/receivers, a temperature sensor, and various other components are mounted on the board. The dimensions of the boards for 3 (4) tube layers are  $11.2 \times 9.3$  cm  $(11.2 \times 10.9$  cm).

**Figure 12.** The mezzanine board contains three 8 channel ASD chips, a 24 channel time digitizer called the AMT, 3.3V power regulators, protection circuitry, connectors that accept the wire signals and a header for the cable to the readout logic.

**Figure 13.** A mezzanine board for use on a three tube layer MDT chamber. The input protection circuitry is on the left, the three ASD chips in the middle, and the AMT chip plus the CSM cable connector are on the right.

**Figure 14.** The input protection components on both the hedgehog board and the mezzanine board limit the pulse current into the amplifier.

The chamber input signals are carried in groups of eight from the signal hedgehog boards. Extensive protection against damage from HV discharges in the tubes is provided in several stages as shown figure 14. The hedgehog board has a 10  $\Omega$  series through-hole 1/4 W resistor. It was found during testing that the inductance provided by the leads of the through-hole component was essential to limit the pulse current to the mezzanine board in the event of an HV breakdown. On the mezzanine board, there are two stages of series resistors and back-to-back diodes to ground. The 20  $\Omega$  value of the series resistors was chosen as a compromise between increased series noise and pulse current reduction. Finally, the MDT-ASD chip itself contains integral protection diodes to limit input transients. With this protection scheme the MDT electronics were demonstrated to be robust against an indefinite number of full HV discharges.

Each ASD chip processes signals from eight MDT tubes, providing eight LVDS outputs to the TDC. These LVDS signals are also available on a small header on the mezzanine board for diagnostics. The TDC time-stamps the output pulses of the ASD using a clock and an encoded trigger, which are received serially on two LVDS pairs from the CSM. The output data and a strobe signal associated with these data are also carried on LVDS pairs between the TDC and CSM. Finally, a calibration pulse trigger signal is received from the CSM on an LVDS pair, and is buffered, and distributed to the ASDs by the TDC.

The programmable parameters for both the ASD and the TDC are initialized using the JTAG protocol. The three ASDs on each mezzanine board are connected in daisy-chain fashion, and are controlled by interface logic on the TDC. The TDC in turn is connected to a JTAG port controlled by the CSM.

A shielded ribbon cable with 20 twisted pairs connects the mezzanine board with the CSM transmitting the digital signals discussed above. A list of the cable lines is given in table 6. In addition to the digital data, four pairs of the cable are used to supply analog power to the mezzanine board and three separate pairs are used to for digital power. The cable also carries both voltage read lines and the signal from a TMP37 [27] linear temperature sensor on the mezzanine. These are digitized by ADCs on the CSM.

The analog and digital supply voltages  $AVdd_{in}$  and  $DVdd_{in}$  are supplied by a common source on the CSM. However, to minimize noise the corresponding grounds are kept separate, including separate ground planes for the digital and analog portions of the mezzanine board. Both analog and digital input power are each protected by a 1.5 A fuse and regulated at 3.3 V by an LP3964-3.3 linear voltage regulator [28]. The currents for the analog and digital supplies are 0.27 and 0.13 A, yielding a total consumption of 1.6 W at 4 V (for more detail on the power consumption see table 3 in section 1.3).

**Table 6.** Pin allocation of the mezzanine board. The resistance of the 40-wire cable is  $0.32~\Omega/m$  per wire. Cable lengths on most MDT chambers range from 0.33~m to 1.33~m. If CSMs are located outside the chamber (e.g. BIS, BEE) cable lengths run up to 5~m.

| pin nı     | ımber      | function                                  | signal | destination |

|------------|------------|-------------------------------------------|--------|-------------|

| 1, 3, 5, 7 | 2, 4, 6, 8 | AVdd <sub>in</sub> (4 V); analog ground   | DC     | AVdd reg.   |

| 9          | 10         | calibration strobe input to ASDs          | LVDS   | ASDs        |

| 11         | 12         | temperature sensor; analog ground         | DC     | CSM         |

| 13         | 14         | regulated analog volt. (3.3V); anlg. grd. | DC     | CSM         |

| 15         | 16         | regulated digital volt. (3.3V); dig. grd. | DC     | CSM         |

| 17, 19, 21 | 18, 20, 22 | DVdd <sub>in</sub> (4 V); digital ground  | DC     | DVdd reg.   |

| 23         | 24         | master reset; digital ground              | CMOS   | AMT         |

| 25         | 26         | serial data out from AMT                  | LVDS   | CSM         |

| 27         | 28         | system clock input to AMT                 | LVDS   | AMT         |

| 29         | 30         | encoded control input to AMT              | LVDS   | AMT         |

| 31         | 32         | serial strobe out from AMT                | LVDS   | CSM         |

| 33         | 34         | JTAG TMS                                  | CMOS   | AMT         |

| 35         | 36         | JTAG TCK                                  | CMOS   | AMT         |

| 37         | 38         | JTAG TDI                                  | CMOS   | AMT         |

| 39         | 40         | JTAG TDO                                  | CMOS   | CSM         |

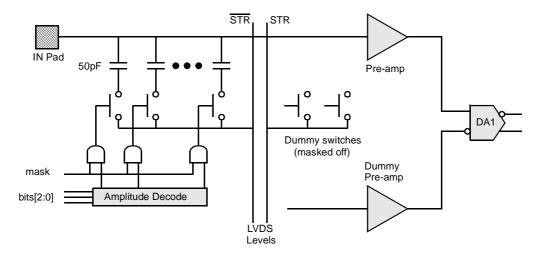

Figure 15. Block diagram of one ASD channel.

# 2.2.1 Amplifier Shaper Discriminator (MDT-ASD chip)

A block diagram of one of the eight channels in the MDT-ASD chip [29] is shown in figure 15 and its specifications are listed in table 7. Each channel consists of a differential input stage, a tail cancellation shaper, a discriminator, a gated integrator, output control logic and an LVDS output driver all running within a 3.3V supply.

The input stage is a pair of low noise cascode pre-amplifiers of moderately low input impedance ( $<100~\Omega$ ) for efficient charge collection from the relatively high impedance (383  $\Omega$ ) MDTs. The

Table 7. ASD specifications.

| Power supply                        | 3.3 V                                      |

|-------------------------------------|--------------------------------------------|

| Pre-amplifier input impedance       | 100 Ω                                      |

| Pre-amplifier noise resistance      | $< 100 \Omega$                             |

| Discriminator time walk             | < 500 ps for the entire input signal range |

| Pre-amplifier peaking time          | approximately 5 ns                         |

| Power consumption                   | 30 mW per channel → 240 mW per chip        |

| Channels per chip                   | 8                                          |

| Minimum pulse spacing of ASD output | 10 ns                                      |

Figure 16. Cascode pre-amplifier schematic.

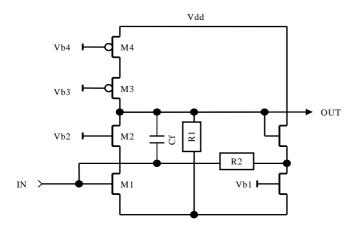

pre-amplifier shown in figure 16 is a low-noise design such that the noise of the system is dominated by the terminating resistor at the far end of the drift tube. The differential input provides high common-mode rejection of noise pick up at the input.

The tail cancellation shaper is a two-stage pole/zero network, which also provides the gain necessary at the discriminator input. Each pole/zero stage is characterized by a pole/zero ratio, which is fixed by design, and a single programmable time constant. Thus changes in drift gas composition can be accommodated within certain limits. In response to a delta function test pulse, the signal peaking time at the discriminator input is in the range of 10-12 ns.

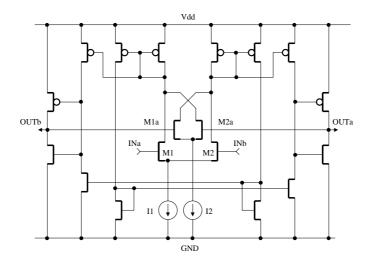

The discriminator is a three-stage design with programmable hysteresis as shown in figure 17. The shaper output is AC-coupled onto the differential pair (M1, M2). Two current mirror "loops" provide differential outputs, which are converted to low-impedance outputs by inverters at OUTa and OUTb. Positive feedback is provided by pair (M1a, M2a) with a programmable current source (I2) which allows for adjustable hysteresis. This design provides fast switching and a time walk which is <500 ps over the dynamic range of the MDT signals.

The gated integrator is controlled by a one-shot which is initiated by the switching of the discriminator and covers the leading edge of the pulse. The charge contained in the leading edge is stored on a capacitor and then run down by the usual Wilkinson technique. The gate width is of

Figure 17. CMOS discriminator with programmable hysteresis.

order 8-45 ns and the rundown of order 100 ns to provide approximately seven bits of resolution. This time-encoded charge is used off-line as a correction for time slewing and enhances the leading-edge spatial resolution by about 20  $\mu$ m, as shown in figure 8.

The output logic block shown in figure 15 provides two modes of operation. The first mode is time-over-threshold (TOT mode) where the output logic signal is forced high as long as the MDT shaped signal is above a fixed threshold. Ideally, this starts on arrival of the first few electrons at the anode wire and ends shortly after the last electrons arrive from the tube wall. In practice, the clumpiness of the primary ionization results in multiple crossings of the discriminator during this time. In the second mode of operation (ADC mode) the fixed current rundown of the charge on the capacitor of the Wilkinson integrator determines the width of the output pulse.

The criteria for selecting one of the two options are the following:

- At the start-up of the experiment when data rates are low, the leading and trailing edges (TOT mode) can be used. The correlation of the trailing edge and the bunch-crossing time is useful for checks on trigger matching and relative timing of different tubes.

- Once the system is understood, achieving optimal spatial resolution is the main goal. At this stage, ADC mode will be appropriate with leading-edge timing and the charge being read. At the nominal LHC luminosity this mode of operation will be used.

The programming of the ASD is done via a JTAG serial string that is passed from the CSM via the TDC chip. The following parameters can be adjusted: discriminator threshold and hysteresis, Wilkinson ADC gate width and discharge rate, dead-time, channel mode (active, held high, off), chip mode (TOT or ADC), calibration channel mask and calibration pulse height. More details on the setting of these parameters can be found in the ASD Users Manual [29].

This ASD chip was developed using the MOSIS fabrication service. The prototype chips were submitted to the HP 1.2 $\mu m$  and HP 0.5 $\mu m$  n-well processes. The latter process was used for the final device.

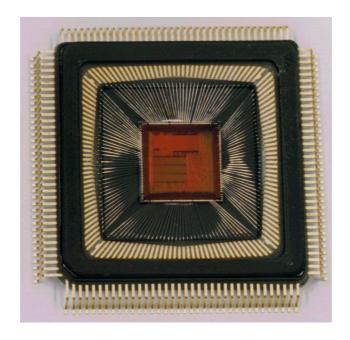

Figure 18. Photograph of the AMT-3 chip.

# 2.2.2 Time to Digital Converter (AMT-3 chip)

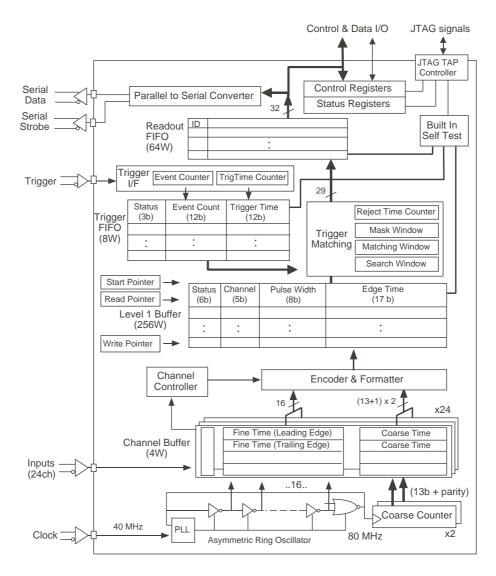

The AMT-3 (ATLAS Muon TDC) chip as shown in figure 18 was fabricated in the Toshiba 0.3 micron CMOS gate-array process (Toshiba TC220G). It performs the required time measurements on 24 channels coming from three ASD chips. Design requirements [30] and Production Readiness Review documents [31] are available for the AMT-3 as well as a detailed chip description and operating manuals [32–34]. Figure 19 shows a block diagram of the AMT-3 chip. The buffering scheme is entirely data driven to avoid large amounts of memory per channel. The AMT specifications are summarized in table 8.

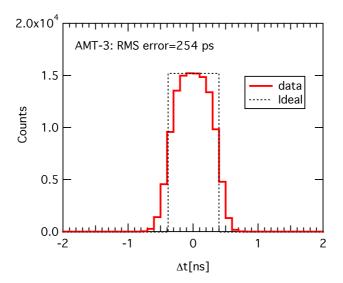

The AMT has a PLL (Phase Locked Loop) circuit which generates an 80 MHz clock from the 40 MHz LHC clock. A voltage controlled oscillator (Asymmetric Ring Oscillator) in the PLL consists of 16 stages of variable delay elements. Gate delay variations as function of process parameters, temperature and supply voltage are stabilized with the PLL. Sixteen timing signal taps, with a delay of 0.78 ns per stage, are derived from the oscillator. Resolution of the time measurement is shown in figure 20 and is about 250 ps, which includes a digitization uncertainty of 226 ps.

Time measurements on a channel are stored in a channel buffer which is four words deep and capable of storing two leading and two trailing edges or four leading or trailing edges. At the output of the channel buffers, leading and trailing edges are paired and written to a common Level-1 (L1) buffer (256 words deep).

The Level-1 trigger information from the central trigger processor enters the AMT-3 via a trigger FIFO which is eight words deep to accommodate multiple triggers arriving within a short time interval. The AMT-3, being data-driven, collects all pulse edges as they arrive independent of its current trigger state. Trigger signals are required to arrive after all hits are collected and stored in the L1 buffers. To provide for flexible hit selection, the AMT-3 contains programmable registers that specify the window for hit selection relative to the trigger arrival time.

**Figure 19.** Block diagram of the AMT-3 chip.

The association of hits stored in the L1 buffer to a given trigger is done via a matching function. The basic feature of this matching function is to search for hits within a trigger-specified time window. This time window is offset to begin at trigger-time and is adjusted to span the maximum drift time. The matching function can also look for hits in a time window preceding the matching window, which may be important for pattern recognition. The presence of any prior hits is signaled in a common output word which contains a flag bit for each channel. All time windows are programmable.

The matched data are stored in a readout FIFO, and are then transferred to the CSM using the serial data and strobe lines. Each serial data word has a one start bit, 32 data bits, one parity bit and two stop bits. The strobe line is either changed in each clock cycle, or changes according to the Data-Strobe (DS) protocol.

Initial setup and debugging are done using the JTAG protocol. There are 22 control and status registers, each with 12 bits. Many internal registers are also accessible via JTAG for debugging

Table 8. TDC Specifications.

| m 1 1                                            |                                             |

|--------------------------------------------------|---------------------------------------------|

| Technology                                       | 0.3 μm CMOS Sea-of-Gate                     |

| Gate size                                        | 110 kgates used (300 kgates master)         |

| Number of input channels                         | 24                                          |

| Signal input                                     | LVDS (100 $\Omega$ termination)             |

| Input clock frequency                            | 40.08 MHz                                   |

| Time bin size                                    | 0.78 ns/bit                                 |

| Time resolution                                  | 250 ps RMS                                  |

| Integral/differential non linearity              | <80 ps RMS                                  |

| Dynamic range                                    | 17 bits ( $\pm 50us$ with trigger matching) |

| Minimum pulse width accepted                     | 5 ns                                        |

| Minimum time between pulses accepted             | 5 ns                                        |

| Maximum rate where loss of data is negligible    | 400 kHz                                     |

| Maximum trigger rate for negligible trigger loss | 200 kHz                                     |

| First-level buffer                               | 256 words                                   |

| Readout FIFO                                     | 64 words                                    |

| Trigger FIFO                                     | 8 words                                     |

| Serial output                                    | 10-80 Mbps, DS or Clock protocol            |

| Parallel output                                  | 32 bits                                     |

| Power supply                                     | 3.3 V                                       |

| Power consumption                                | <15 mW/channel (<360 mW/chip)               |

| Package                                          | 144 pin plastic QFP                         |

**Figure 20.** Resolution of the AMT-3 chip.

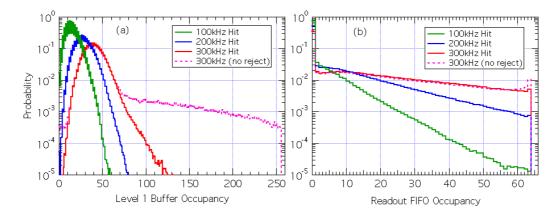

**Figure 21.** Occupancy (words) of (a) the L1 buffer (256 words maximum) and (b) the readout FIFO (64 words maximum) for different MDT hit rates. The data have been simulated with a serial readout speed of 80 Mbits/sec and a trigger rate of 100 kHz. Old hits are removed from the L1 buffer when the readout FIFO becomes full. If this rejection feature is disabled, the occupancy reaches maximum L1 buffer size.

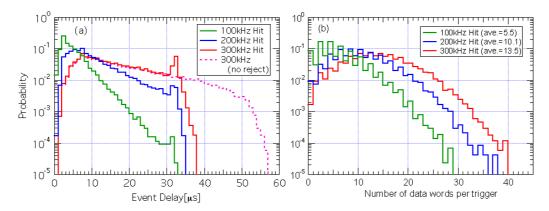

**Figure 22.** (a) Event delay (trigger to readout time) distribution and (b) number of data words (32 bits) per trigger for different MDT counting rates. The simulation conditions are the same as in the previous figure. The hit rejection feature reduces the maximum event delay to less than 40  $\mu$ sec. An average of 10 data words per AMT is expected at a hit rate of 200 kHz per tube.

purposes. Programming of the ASD chips is also done through the AMT-3 via the JTAG interface.

The AMT-3 architecture has been extensively simulated to investigate the possible loss of hits. A serial readout speed of 80 Mbits/sec was used along with a trigger rate of 100 kHz together with the standard output mode, namely each event includes a header and a trailer word plus a conditional mask word. Figure 21 shows the occupancy of the L1 buffer and the readout FIFO for different MDT count rates. The occupancy of the L1 buffer is reduced by enabling the rejection of old hits whenever a readout FIFO full condition occurs. This rejection feature is also important to avoid long event delays (trigger to readout time).

Figure 22 shows the event delay distribution and number of data words (32 bits) per trigger for different MDT count rates. The maximum delay is limited to less than 40  $\mu$ s with FIFO-full hit rejection enabled. The average number of data words is about ten at 200 kHz hit rate (which includes the 3 control words). The buffer becomes full for input rates greater than 200 kHz due to

the bandwidth limitation of the readout serial link. Data loss is about 0.7% and 5.3% for 200 kHz and 300 kHz hit rates respectively. This can be reduced by disabling the hit rejection feature, but this in turn increases the maximum event delay.

The AMT-3 architecture has also been simulated and tested to ensure that all hits within the programmed time window are appropriately digitized and sent to the CSM. If a buffer overflow does occur and one or more hits is lost, then a flag bit is set in the next TDC data word that is transmitted. The time elapsed between the previous good hit and a good hit with this flag set can be considered as a dead period for the TDC digitization.

The simulations described above were carried out using Verilog codes. The codes were initially written at the behavioral level, but eventually the tests were done with gate level codes corresponding to the actual AMT-3 chip. The same codes were also used in mass production testing to select good AMT-3 chips.

# 2.3 On-chamber multiplexer - Chamber Service Module (CSM)

The on-chamber multiplexer known as the Chamber Service Module (CSM) is composed of a passive interconnect board and an active board which together have the following functions:

- Receiving the trigger, timing, and control signals from the TTC system.

- Delivering the TTC signals to all mezzanine boards.

- Multiplexing all serial data from the mezzanine boards to a single output stream.

- Delivering the output data stream to a gigabit fiber link connected to the MROD.

- Providing the ELMB monitoring function of voltage and temperature sensing.

- Routing the JTAG signals from the ELMB to the mezzanine boards.

All connections to the active CSM board are routed through the passive board except the optical fiber connections from the TTC and to the MROD, which are made directly to the active board.

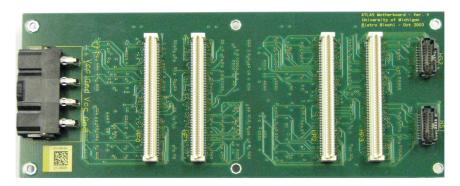

### 2.3.1 The passive interconnect

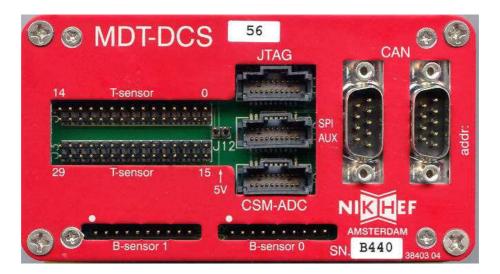

The passive interconnect must provide for connection to the largest chambers which have eighteen mezzanine boards. These individual mezzanine boards are attached to the passive board via a high-density 40-pin twisted pair cable with 0.625 mm spacing. This cable delivers the supply voltage (nominally 4 V) to the analog and digital 3.3 V regulators on the mezzanine board, carries the 40.08 MHz crossing clock, the encoded commands to the board, receives the serial data from the AMT, and routes the sense lines from the mezzanine board voltages and temperature sensors to the analog multiplexer on the CSM, which is read out by the ELMB. Details of the signal allocation of the cable wires are given in table 6. The connections to the ELMB are opto-isolated and are provided by two ribbon cables with high-density 20-pin connectors mounted on the side of the interconnect board away from the chamber. This signal path provides for CSM initialization, conditions monitoring, and fault recovery. The passive board presents all signals to the active board, the actual CSM, via four high-density board to board connectors of 140 pins each. The interconnect board is shown in figure 23 and figure 24.

Figure 23. The passive interconnect board rear showing the eighteen mezzanine board connectors.

**Figure 24.** The passive interconnect board top showing the board to board connectors that route the mezzanine board signals to the active CSM. Power enters the passive board through the 4-pin connector at the left and is directed to the CSM and all mezzanine boards. The voltage supplied to the CSM is approximately 4 V, and an eighteen mezzanine board chamber draws about 8.3 A.

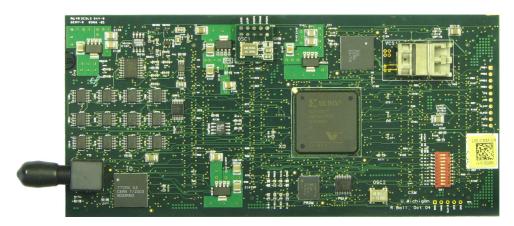

# 2.3.2 The active CSM multiplexer

The active CSM, represented in the block diagram of figure 25, incorporates:

- A medium-sized FPGA

- A TTC optical receiver and its TTCrx decoder chip [35]

- A gigabit optical encoder chip (GOL) [36]

- A VCSEL laser diode optical transmitter [37]

- Several voltage regulators

- 10 MHz and 50 MHz oscillator chips

- A PROM for FPGA configuration

- Several TTL fanout chips for JTAG control signals

- A 64-channel analog multiplexer to measure voltages and temperatures on the CSM and mezzanine boards

**Figure 25.** A block diagram of the on-chamber multiplexer showing its relationship to the mezzanine boards, ELMB, TTC, and MROD. Except for the TTC fiber and the fiber to the MROD all connections to the CSM are through the passive interconnect.

**Figure 26.** A photo of the CSM showing the TTC fiber connector at the left and the MROD fiber connector at the right. The medium sized Xilinx FPGA in the center provides the multiplex function and the cluster of small chips on the left constitutes the analog multiplexer for voltage and temperature monitoring.

• Opto-isolators to isolate the CSM ground from that of the ELMB.

A photo of the CSM board is shown in figure 26.

The active multiplexer has been implemented in a Virtex-II FPGA, coded in VerilogHDL, and simulated for various trigger and data rates [38]. The internal design and output bandwidth of the CSM has been arranged so that all data from up to eighteen mezzanine boards can be processed without data loss. The output bit rate of the AMT-3 operating at 80 MHz requires 0.45  $\mu$ s to transfer a data word plus parity, start, and stop bits. These words (eighteen maximum in 32 bit

format) are delivered to the MROD in eighteen time slots along with a synchronization word and two words of optical link idle codes. With the CSM to MROD link operating at a 50 MHz 32 bit word rate, these 21 words can be sent to the MROD in 0.42  $\mu$ s. With modest buffering, no data loss due to buffer overflow is possible. The trigger to readout latency is mostly due to the AMT-3 and serial link speed. However, the six pipeline processing steps of the CSM and the polling design of the output sequencing implies an additional contribution to the latency of approximately 0.5  $\mu$ s. Transmission delay in the approximately 100 m long optical fiber between the chamber-mounted CSM and the MROD in the electronics cavern will also add to the latency.

The CSM has two modes of operation, an asynchronous 40 MHz bit rate from the AMT coupled with a 25 MHz 32 bit word rate to the MROD or 80 MHz bit rate from the AMT with a 50 MHz 32 bit word rate to the MROD. In both cases no data loss is possible since the output rate can accommodate the sum of all eighteen (mezzanine boards) input rates with sufficient margin. A small add-on board with a 50 MHz crystal oscillator was added to the CSM to accomplish operation at the higher speed. (The board is labeled "OSC1" and can be seen at the upper edge of the photo in figure 26.) Normal operation will be at this higher rate. If a 40 MHz bit rate from mezzanine boards is sufficient to handle the data from chambers at large radius from the collision point, the 50 MHz frequency can be divided by 2 in the FPGA. Only the end-cap chambers have been fully outfitted with add-on boards and can operate at 50MHz. CSMs without the add-on board must operate at the lower readout speed. CSMs with the add-on board can operate at either speed.

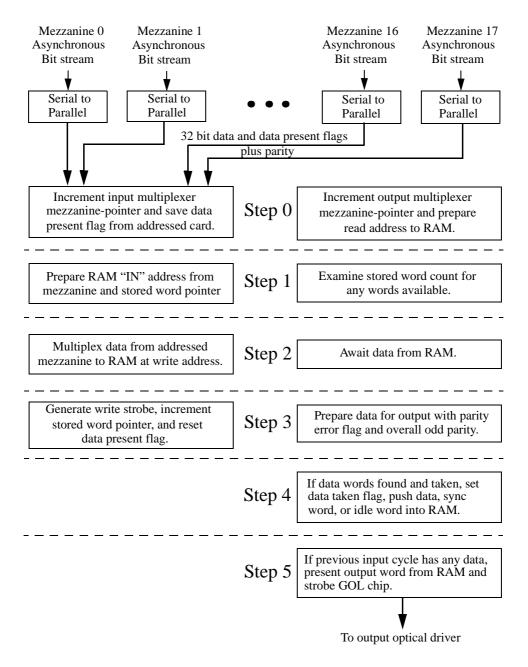

The CSM accomplishes its tasks in six pipelined steps as illustrated in figure 27. In the first step, eighteen independent circuits sample the eighteen incoming bit streams from the mezzanine boards and perform the serial-to-parallel conversion. The asynchronous protocol requires a single start bit, 32 data bits, a parity bit, and 2 stop bits for each data word from the AMT. The CSM contains two polling loops, one examining the input from the 18 mezzanine cards and one sequencing through the 21 steps of output to the MROD. A dual-ported RAM buffers the information flow between these multiplexers which run at different speeds. The polling loops are not synchronized but the higher speed of data removal than entry guarantees that no pileup will occur in the RAM. If no data is available from a mezzanine, nothing is stored. The output loop operates as time division multiplexer and must fill each time slot of the 21 word sequence. Thus, when no AMT data word is available from a given mezzanine board, a dummy word with a unique identifier is sent. In order to sustain synchronization of this polling cycle, the CSM inserts one word per cycle with a second specific identifier that indicates the start of a polling cycle. At the end of the polling cycle, the CSM inserts two words of optical link synchronization codes. The presence of these words guarantees that the optical transmitter and receiver will be resynchronized automatically after each polling cycle should it loose synchronization at any time.

The parameters of the CSM are loaded via JTAG protocol in a series chain that includes the on-board PROM containing the FPGA code, the FPGA boundary scan and the CSM constants. Under control of the CSM the series may additionally include the GOL boundary scan and parameters, the TTCrx boundary scan, and the JTAG strings of up to eighteen Mezzanine boards [13]. The TTCrx chip does not permit its parameters to be included in the JTAG chain. To load the TTCrx with the needed setup constants, the data are included in the CSM parameters and sent to the TTCrx with the CSM emulating a PROM when viewed by the TTCrx. The GOL parameters used are the default settings, therefore the GOL need not be included in the JTAG chain. For "cold start" programming

**Figure 27.** The steps in the CSM pipeline for both input and output polling. A dual-ported RAM provides for data flow between these loops which operate at different speeds.

of the PROM or FPGA, the ELMB can force the JTAG loop to include only the PROM and FPGA prior to a new firmware download of the CSM. The ELMB can also force a reload of the FPGA from PROM for a "warm start" of the CSM.

One important initialization step for the CSM involves providing the CSM with the choice of clock phase to be used to sample the incoming data from each of up to eighteen mezzanine boards. The AMT chips transmit their serial data based on the clock signal provided by the CSM. Mezzanine boards reside electrically at the end of cables ranging from 0.3 m to 5 m. The return

phase from each AMT is thus influenced by the length of the connecting cable. To accommodate this variation, the CSM forms four clock phases (0, 90, 180, 270°) from the outgoing clock sent to all mezzanine boards. The appropriate phase must be selected for each mezzanine board (AMT). The CSM provides two means for the selection of the best phase. It can be instructed to dynamically sample the data from each mezzanine board and select the candidate phase to use or it can be instructed to use a specific phase for each of the eighteen mezzanine boards.

In the first case, the CSM sends a few internally generated triggers to the AMT and examines the data arriving from each AMT, flagging where data transitions appear in the intervals between the four clock phases. When the triggered events are all received by the CSM, the flags are examined. Most often only one flag is set and the selection of interval is obvious. Since the delay of the returning mezzanine data can be arbitrary, returning data sometimes appears in two adjacent intervals. In this case the later interval is selected. This selection is chosen since for the synchronous flip-flops of the FPGA, setup time is required but hold time is not. Once the latest (or only) interval where transitions are seen is determined, the clock edge 180 degrees after the starting point of the interval is selected.

In the second case, the database is queried to provide the selection and the previously sampled and stored phase for each mezzanine board is transmitted to the CSM over JTAG. In all cases, the AMT is instructed to not send a clock with the data. This eliminates the returning data strobe as a source of crosstalk which might interfere with data sampling. Operation in the self synchronous mode is possible since the frequency of the AMT data is phase locked to the frequency of the clock signal provided by the CSM.

### 2.4 Monitoring and control - Embedded Local Monitor Board (ELMB)