# **HOTLink™** Design Considerations

# **Application Note Overview**

The HOTLink™ family of data communications products provides a simple and low-cost solution to high-speed data transmission. While these products are easy to use, the methods used to connect them to high-speed serial interfaces are often not intuitive. This document provides a basic level of explanation of the parallel and serial interface characteristics, and provides some cookbook solutions for interfacing them to different types of parts and media.

# **Primary Topics**

The primary topics covered in this application note are:

- HOTLink Overview

- HOTLink Serial Signal Characteristics

- Terminating HOTLink Serial Signals

- · Interfacing to HOTLink

- · Serial Link Support Components

### **HOTLink Overview**

#### **HOTLink Features**

- · Fibre Channel compliant

- IBM® ESCON™ compliant

- DVB-ASI compliant

- ATM compatible

- 8B/10B-coded or 10-bit unencoded

- 150- to 400-Mbps data rate

- TTL-synchronous I/O

- · No external PLL components

- Triple ECL 100K serial outputs

- Dual ECL 100K serial inputs

- Low power: 350 mW (Tx), 650 mW (Rx)

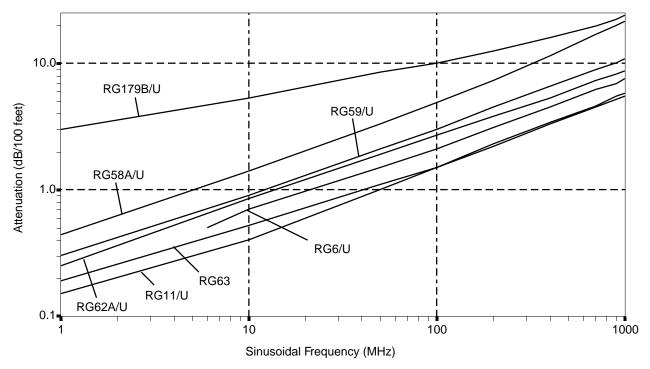

- Compatible with fiber-optic modules, coaxial cable, and twisted-pair media

- Built-In Self-Test (BIST)

- Single +5V supply

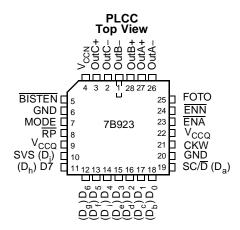

- 28-pin SOIC/PLCC/LCC

- 0.8μ BiCMOS

#### **Functional Description**

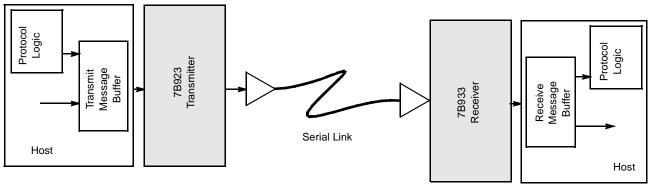

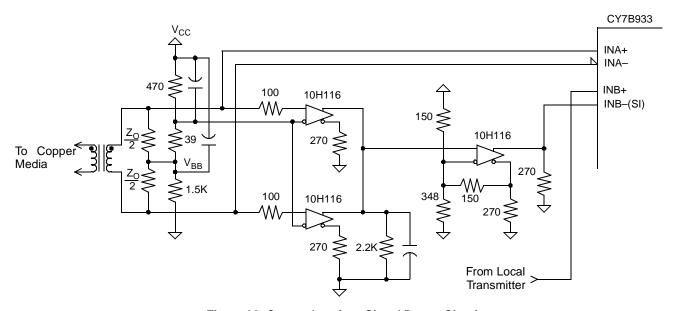

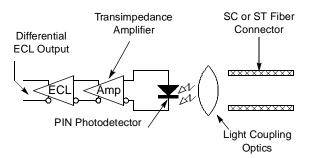

The CY7B923 HOTLink Transmitter and CY7B933 HOTLink Receiver are point-to-point communications building blocks that transfer data over high-speed serial links (fiber-optic, coax, and twisted/parallel-pair) at 150- to 400-Mbits/second. *Figure 1* illustrates typical connections to host systems or controllers.

Eight bits of user data or protocol information are loaded into the HOTLink Transmitter and are encoded into a 10-bit transmission character. The transmission character is shifted serially out of the three differential positive ECL (PECL) serial ports at the bit-rate (which is ten times the character-rate).

The HOTLink Receiver accepts the serial bit stream at its differential line receiver inputs and, using a completely integrated phase-locked-loop (PLL) clock synchronizer, recovers the timing information necessary for data reconstruction. The bit stream is deserialized, decoded, and checked for transmission errors. The recovered character is presented in parallel to the receiving host along with the synchronized character-rate clock.

The 8B/10B encoder/decoder (Reference 1, 2) can be disabled in systems that already encode or scramble the transmitted data. Signals are available to create a seamless interface with both asynchronous FIFOs (i.e., Cypress's CY7C42X) and clocked/synchronous FIFOs (i.e., Cypress's CY7C44X/46X). A BIST pattern generator and checker allows testing of the transmitter, receiver, and the connecting link as a part of a system diagnostic check.

HOTLink devices are ideal for a variety of applications where a parallel interface can be replaced with a high-speed point-to-point serial link. Applications include interconnecting workstations, servers, mass storage, and video transmission equipment.

Figure 1. HOTLink System Connections

### **CY7B923 HOTLink Transmitter Description**

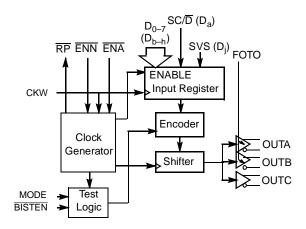

The function of the HOTLink Transmitter is to convert character-rate parallel data into a high-speed serial data stream. A logic block diagram of the transmitter is shown in *Figure 2*.

Figure 2. CY7B923 Transmitter Logic Block Diagram

#### Input Register

The Input Register holds the data to be processed by the HOTLink Transmitter and allows the input timing to be made consistent with standard FIFOs. The Input Register is clocked by CKW (clock write) and loaded with information on the D<sub>0-7</sub>, SC/ $\overline{D}$  (special character/data select), and SVS (send violation symbol) pins. Two enable inputs ( $\overline{ENA}$  and  $\overline{ENN}$ ) allow the user to choose when data is to be sent. Asserting  $\overline{ENA}$  (enable, active LOW) causes the inputs to be loaded on the rising edge of CKW. If  $\overline{ENN}$  (enable next, active LOW) is asserted when CKW rises, the data present on the inputs at the *next* rising edge of CKW is loaded into the input register. These two enable inputs allow proper timing and function for compatibility with either asynchronous FIFOs or clocked/synchronous FIFOs without external logic.

In BIST mode, the Input Register becomes a pattern generator by logically converting into a linear-feedback shift-register (LFSR). When enabled, this LFSR generates a 511-character sequence that includes all Data and Special Character codes, including the explicit violation symbols. This pattern provides a predictable but pseudo-random sequence that can be matched to an identical LFSR in the HOTLink Receiver. For additional information see the Cypress Semiconductor application note "HOTLink Built-In Self-Test."

# Encoder

The Encoder transforms the input data, held by the Input Register, into a form more suitable for transmission on a serial interface link. The code used is specified by the ANSI X3.230-1994 Fibre Channel standard (Reference 3) and the IBM ESCON channel (Reference 4) (code tables are available in the CY7B923/CY7B933 data sheet). The eight  $D_{0-7}$  data inputs are converted to a 10-bit Transmission Character, as directed by the state of the SC/ $\overline{D}$  input. If SC/ $\overline{D}$  is HIGH, the data inputs represent a control code and are encoded using the Special Character code tables. If SC/ $\overline{D}$  is LOW, the data inputs are converted using the Data code table. If a character-time passes with the inputs disabled, the Encoder outputs a Special Character Comma (K28.5 or SYNC) to maintain link

synchronization. The SVS input forces the transmission of a specified Violation symbol to allow the user to check error handling logic in a system controller.

The 8B/10B coding function of the Encoder can be bypassed for systems that include an external encoder or scrambler as part of the controller. This bypass capability is controlled by setting the MODE select pin HIGH. When in Bypass mode,  $D_{a-j}$  (note that bit order is specified by the Fibre Channel 8B/10B code) become the ten inputs to the Shifter, with  $D_a$  being the first bit to be shifted out.

#### Shifter

The Shifter accepts parallel data from the Encoder once each character-time and shifts it to the serial interface output buffers using a PLL multiplied bit-clock that runs at 10 times the character-clock (CKW) rate. Timing for the parallel transfer is controlled by the counter included in the Clock Generator, and is not affected by signal levels or timing at the input pins.

#### OutA, OutB, OutC

The serial interface ECL output buffers (100K signal levels referenced to +5V) are the drivers for the serial media. They are all connected to the Shifter and present the same serial data. Two of the output pairs (OUTA± and OUTB±) are controlled by the FOTO input and can be disabled by the system controller to force a logical zero (i.e., "light off") at the outputs. The third output pair (OUTC±) is not affected by FOTO and supplies a continuous data stream suitable for loop-back testing of the subsystem.

OUTA± and OUTB± respond to FOTO input changes within a few bit-times. However, since FOTO is not synchronized with the transmitter data stream, the outputs are forced off or turned on at arbitrary points in a transmitted character. This function is intended to augment an external laser safety controller and as an aid for Receiver PLL testing.

In wire-based systems, control of the outputs may not be required, and FOTO can be strapped LOW. The three output pairs are intended to add system and architectural flexibility by offering identical serial bit-streams with separate interfaces for redundant connections or for multiple destinations. Unneeded outputs can be left open or wired to  $V_{CC}$  to disable and power down the unused output circuitry.

# Clock Generator

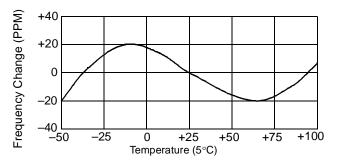

The clock generator is an embedded phase-locked loop (PLL) that takes a character-rate reference clock (CKW) and multiplies it by ten to create a bit-rate clock for driving the serial shifter. The character-rate reference comes from CKW, the rising edge of which clocks data into the Input Register. This clock must be a crystal-referenced (or other high-stability) pulse stream that has a frequency between the minimum and maximum specified for the HOTLink Transmitter/Receiver pair. Signals controlled by this block form the bit-clock and the timing signals that control internal data transfers between the Input Register and the Shifter.

The read pulse  $(\overline{RP})$  is derived from the feedback counter used in the PLL multiplier. It is a character-rate pulse stream with the proper phase and pulse widths to allow transfer of data from an asynchronous FIFO. Pulse width is independent of CKW duty cycle, since proper phase and duty cycle is maintained by the PLL. The RP pulse stream ensures correct data transfers between asynchronous FIFOs and the transmitter input latch with no external logic.

#### Test Logic

Test Logic includes the initialization and control for the built-in self-test (BIST) generator, the multiplexer for Test mode clock distribution, and control logic to properly select the data encoding. Test Logic is discussed in more detail in the CY7B923/CY7B933 HOTLink data sheet.

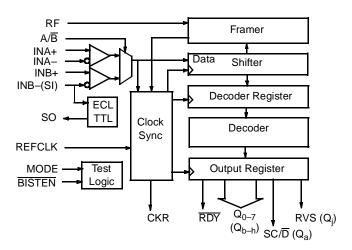

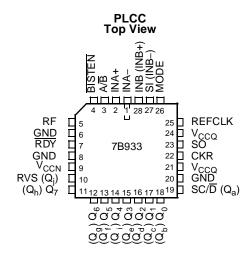

#### CY7B933 HOTLink Receiver Description

The function of the HOTLink Receiver is to convert a high-speed serial data stream into character-rate parallel data. A logic block diagram of the receiver is shown in *Figure 3*.

Figure 3. CY7B933 Receiver Logic Block Diagram

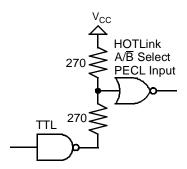

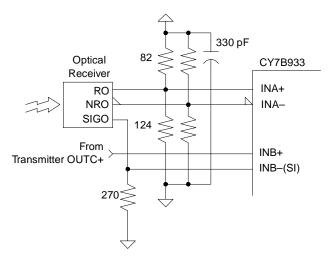

# Serial Data Inputs

The HOTLink Receiver has two differential line receivers (INA± and INB±) that can be selected as inputs for the serial data stream. INA $\pm$  or INB $\pm$  is selected with the A/ $\overline{B}$  input. INA $\pm$  is selected when A/B is HIGH and INB $\pm$  is selected when  $A/\overline{B}$  is LOW. The threshold of  $A/\overline{B}$  is compatible with ECL 100K signals. TTL logic elements can be used to select the INA± or INB± inputs by adding a resistor voltage divider to a TTL driver connected to A/B (see Figure 35). The differential sensitivity of INA± and INB± will accommodate wire interconnect with filtering losses or transmission line attenuation greater than 20 dB (V<sub>DIF</sub> ≥ 50 mV). These inputs can alternatively be directly connected to fiber-optic interface modules (any ECL logic family, not limited to ECL 100K) with up to 1.2V of differential signal. The common-mode tolerance accommodates a wide range of signal termination voltages. The highest HIGH input that can be tolerated is  $V_{IN} = \bar{V}_{CC}$ , and the lowest LOW input that can be interpreted correctly is  $V_{IN} = GND+2.0V.$

# ECL/TTL Translator

The function of the INB(INB+) input and the SI(INB-) input is determined by the connection on the SO output pin. If the ECL/TTL translator function is not required, the SO output is wired to  $V_{CC}.$  A sensor circuit detects this connection and causes the inputs to become INB± (a differential line-receiver for serial-data input). If the ECL/TTL translator function is required, the SO output is connected to a normal TTL load (typically one or more TTL inputs, but no pull-up resistor) and the inputs become INB (single-ended ECL 100K-level serial-data input) and SI (single-ended ECL 100K-level status input).

This positive-referenced ECL-to-TTL translator is provided to eliminate external logic between an ECL carrier-detect or link status signal and a TTL input in the control logic. The input threshold is compatible with ECL 100K levels (+5V referenced).

#### Clock Sync

The Clock Synchronizer function is performed by an embedded phase-locked loop (PLL) that tracks the frequency of the incoming serial bit-stream and aligns the phase of its internal bit-rate clock to the serial data transitions. This block contains the logic to transfer the data from the Shifter to the Decode register once every character. The counter that controls this transfer is initialized by the Framer logic. CKR is a buffered output derived from the bit counter used to control Decode register and Output register transfers.

Clock output logic is designed such that when reframing causes the counter sequence to be interrupted, the period and pulse width of CKR is never less than normal. Reframing may stretch the period of CKR by up to 90%, and either CKR pulse width HIGH or pulse width LOW may be stretched, depending on when reframe occurs.

The REFCLK input provides a character-rate reference frequency to improve PLL acquisition time and limit unlocked frequency excursions of CKR when no data is present at the serial inputs. The frequency of REFCLK is required to be within  $\pm 0.1\%$  of the frequency of the clock that drives the transmitter CKW pin.

#### Framer

Framer logic checks the incoming bit-stream for the pattern that determines the character boundaries. This combinatorial logic filter looks for the ANSI Fibre Channel symbol defined as a Special Character Comma (K28.5) (Reference 3). When framing is enabled and this character is found, the free-running bit-counter in the Clock Sync block is synchronously reset to its initial state, thus framing the data on the correct character boundaries.

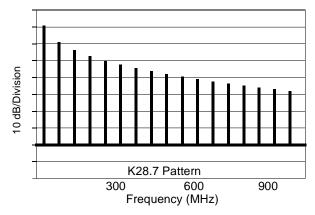

Random errors that occur in the serial data can corrupt some data patterns into a bit-pattern identical to a K28.5, and thus cause an erroneous data-framing error. The RF input prevents this by inhibiting reframing during times when normal message data is present. When RF is held LOW, the HOTLink Receiver deserializes the incoming data without trying to reframe the data. When RF rises, RDY is inhibited until a K28.5 is detected, after which RDY resumes its normal function. While RF is HIGH, it is possible that an error in the serial data could cause misframing, after which all data would be corrupted. Likewise, a K28.7 followed by D11.x, D20.x, or an SVS (C0.7) followed by D11.x will cause erroneous framing. These sequences must be avoided while RF is HIGH.

If RF remains HIGH for greater than approximately 2048 characters, the framer switches to multi-byte framing, requiring two K28.5 Special Characters within a five character span.

#### Shifter

The Shifter accepts serial data from one of the serial data input receivers, one bit at a time, as clocked by the Clock Sync logic. Data is examined by the Framer on each bit, and is transferred to the Decode Register once per character.

### Decode Register

The Decode Register accepts data from the Shifter once per character as determined by the logic in the Clock Sync block. It is presented to the Decoder and held until it is transferred to the Output Register.

#### Decoder

Parallel data is transformed from ANSI Fibre Channel 8B/10B codes (Reference 3) back to "raw data" in the Decoder. This block uses the standard decoder patterns found in the Valid Data Characters and Valid Special Character Codes and Sequences (code tables are available in the CY7B923/CY7B933 data sheet). Data Characters are signaled by a LOW on the SC/D output and Special Characters are signaled by a HIGH on the SC/D output. Unused patterns or disparity errors are signaled as errors by a HIGH on the RVS (Received Violation Symbol) output and by specific Special Character codes.

#### Output Register

The Output Register holds the recovered data ( $Q_{0-7}$ , SC/ $\overline{D}$ , and RVS) and aligns it with the recovered character clock (CKR). This synchronization ensures proper timing to match a FIFO interface or other logic that requires glitch-free and specified output behavior. Outputs change synchronously with the rising edge of CKR.

In BIST mode, this register becomes a pattern generator and checker by logically converting itself into a linear-feedback shift-register (LFSR). When enabled, this LFSR generates a 511-character sequence that includes all Data and Special Character codes, including the explicit violation symbols. This provides a predictable but pseudo-random sequence that can be matched to an identical LFSR in the transmitter. When synchronized, it checks each character in the Decoder with each character generated by the LFSR and indicates errors using RVS. Patterns generated by the LFSR are compared after being buffered to the output pins and then fed back to the comparators, allowing a test of the entire receive function.

In BIST mode, the LFSR is initialized by the first occurrence of the transmitter BIST loop start code D0.0 (D0.0 is sent only once per BIST loop). Once the BIST loop has been started, RVS goes HIGH for pattern mismatches between the received sequence and the internally generated sequence. Code rule violations or running disparity errors that occur as part of the BIST loop do not cause an error indication. RDY pulses high once per BIST loop and can be used to check test pattern progress. The receiver BIST checker can be reinitialized by leaving and re-entering BIST mode.

#### Test Logic

Test Logic includes the initialization and control for the built-in self-test (BIST) checker, the multiplexer for Test mode clock distribution, and control logic for the decoder. Test Logic is discussed in more detail in the CY7B923/CY7B933 HOTLink data sheet.

# **HOTLink Serial Signal Characteristics**

The serial interfaces on the HOTLink Transmitter and Receiver are based on the standard for high-speed digital logic called emitter-coupled-logic or ECL. This form of logic has been used commercially in integrated circuits since the early 1960s, and prior to that it was implemented in discrete form.

ECL is a non-saturating form of digital logic. ECL gets its name from how the emitters of a differential amplifier in the circuit are connected. The main features of this logic family are very high speed, low noise, and the ability to drive low-impedance transmission lines.

In the past, many engineers have avoided ECL as a logic family because it was different from the TLL-compatible families with which they were more familiar. Proper use of ECL requires the understanding and application of transmission lines, line termination, and power supply bypassing. Because of the faster speeds present in the newer TTL-compatible families, these same disciplines are now required for TTL circuits.

# **ECL Signal Level Reference**

The primary differences between ECL and other logic families are the signal levels used to represent the HIGH and LOW logic levels.

In the TTL and CMOS logic families, a LOW is usually some level close to  $V_{SS}$ , and a HIGH is usually some level close to  $V_{CC}$ . The ground or reference point for these measurements is usually the  $V_{SS}$  point, with  $V_{CC}$  set to +5V from that ground reference.

In standard ECL this changes significantly. Instead of having the ground reference at  $V_{SS}$ , it is placed at  $V_{CC}$ . This means that both HIGH and LOW logic levels exist at potentials that are negative with respect to ground. Standard ECL is specified as operating with a negative supply (–4.5V to –5.2V for  $V_{EE}$ ). Since ground is only a reference point, it is also possible to operate ECL with a positive supply. When used in this mode ECL is usually referred to as PECL which means Positive ECL.

# **ECL Basic Switch**

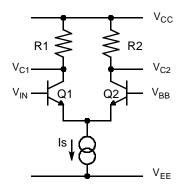

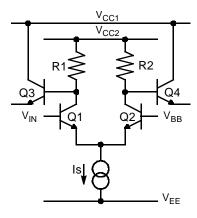

Internally, ECL gates (or switches) operate using a current source whose current is directed through one of two paths to  $V_{CC}$ . A schematic of this basic ECL switch is shown in Figure 4 (Reference 5).

Figure 4. Basic ECL Switch

In this ECL switch, the state of the switch is determined by the voltage drop across R1 and R2. The output signal swing is set by the size of these resistors and the magnitude of the current passed through them.

The base of Q2 is biased at a fixed voltage called V<sub>BB</sub>. This voltage determines at what level of V<sub>IN</sub> on Q1 that the majority of the current flowing in the switch changes from R1 to R2. If V<sub>IN</sub> is set to the same voltage as V<sub>BB</sub>, the current divides

equally between R1 and R2. Increasing  $V_{IN}$  by 125 mV above  $V_{BB}$  causes essentially all the current to flow through Q1 (and hence R1). Lowering  $V_{IN}$  to 125 mV below  $V_{BB}$  causes essentially all the current to flow through Q2. This means that an input swing of as little as 250 mV can cause the ECL gate to switch completely from a 0 to a 1. To provide noise immunity and allow operation over a wide variety of conditions, the actual signal swing specified for ECL signals is around 800 mV.

#### **Emitter-Follower**

The switch shown in *Figure 4* can react very quickly but, because of its high-value resistor pull-ups (R1 and R2), its switching delay varies directly with load capacitance. To allow larger loads to be driven, and to make the output voltages compatible with the input of subsequent gates, additional transistors are added in an emitter-follower configuration as shown in *Figure 5*.

These emitter-follower transistors have a very low on-impedance (5–7 $\Omega$ ). This allows ECL gates to drive transmission lines having impedances at or below 50 $\Omega$ , and can supply load currents of up to 50 mA.

The emitter-follower transistors have an uncommitted emitter as their output. This allows the transistor to source, but not sink, current. This is effectively the opposite of an open-collector output in a TTL part. To allow the output to function correctly, it requires a load that operates as a pull-down.

Figure 5. Buffered ECL Switch

# **ECL Signal Levels**

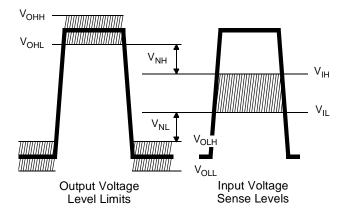

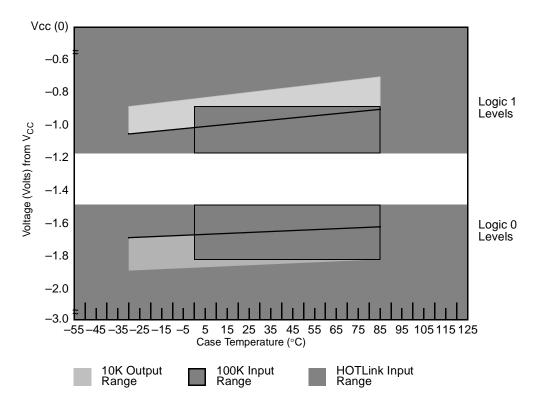

ECL signals operate over a very narrow and tightly controlled range. These signal levels are referenced from the  $V_{CC}$  pins of the parts. *Figure 6* shows the relationships of the different output and input levels for ECL gates. The names of these levels are detailed in *Table 1*.

# ECL Output Signal Levels

ECL outputs are all referenced from V $_{CC}$ . A typical ECL driver has an output-HIGH level (V $_{OH}$ ) of V $_{CC}$  – 0.85V and an output-LOW level (V $_{OL}$ ) of V $_{CC}$  – 1.7V. These typical values are seldom specified for parts because a good design must be done using the range limits for these signals as listed in *Table 1*. Actual values for these levels vary by individual part type and ECL family.

Figure 6. ECL Signal Levels

Table 1. ECL Signal Level Names

| Name             | Description                                                  |

|------------------|--------------------------------------------------------------|

| V <sub>OHH</sub> | Highest Output HIGH Voltage                                  |

| V <sub>OHL</sub> | Lowest Output HIGH Voltage                                   |

| V <sub>OLH</sub> | Highest Output LOW Voltage                                   |

| V <sub>OLL</sub> | Lowest Output LOW Voltage                                    |

| V <sub>IH</sub>  | Lowest Input HIGH Voltage Threshold                          |

| V <sub>IL</sub>  | Highest Input LOW Voltage Threshold                          |

| V <sub>NH</sub>  | High Input Noise Margin (V <sub>OHL</sub> -V <sub>IH</sub> ) |

| V <sub>NL</sub>  | Low Input Noise Margin (V <sub>OLH</sub> -V <sub>IL</sub> )  |

### ECL Input Signal Levels

ECL Inputs are also referenced from V $_{CC}$ . A typical ECL receiver has an input-HIGH (V $_{IH}$ ) threshold of V $_{CC}$ – 1.1V and an input-LOW (V $_{IL}$ ) threshold of V $_{CC}$ – 1.47V. These differences between the output and input HIGH and LOW values translate directly into the usable noise margin (V $_{NH}$  and V $_{NL}$ ) of a system.

#### Viewing ECL Signals

Proper viewing of ECL signals requires use of an oscilloscope and probes with sufficient bandwidth to see the important features of the waveforms. Depending on the speed of the signals being viewed, different scope and probe characteristics are required.

#### Oscilloscope Bandwidth

Oscilloscope bandwidth is not a simple number; it is based on the combined bandwidths of multiple pieces of the measurement system. These can include the oscilloscope, the scope probe amplifier, the probe itself, and possibly other components.

The calculation for bandwidth is based on an inverse sum-of-squares as shown in Equation 1.

$$bw = \frac{1}{\sqrt{\left(\frac{1}{bw_1}\right)^2 + \left(\frac{1}{bw_2}\right)^2}}$$

Eq. 1

Thus a scope with a 1-GHz bandwidth probe using a 1-GHz bandwidth amplifier would only have a usable bandwidth of 700 MHz.

The current ANSI Fibre Channel standard specifies the minimum system bandwidth for testing as 1.8 times the signaling rate. For testing with the HOTLink parts (400 MBaud), this translates to a minimum system bandwidth of 720 MHz. This is translated into a viewable rise time using Equation 2 (Reference 6).

$$t_r = \frac{0.35}{bw}$$

Eq. 2

This means that the oscilloscope and probes, having a 700 MHz bandwidth, can display signals with rise-times no faster than 480 ps, without having more than 3 dB of attenuation.

**Note**: Various scope manufacturers use different conventions to specify bandwidth for their equipment; i.e., specified bandwidth is not necessarily where the displayed waveforms are 3 dB down in amplitude.

#### Scope Probes

Scope probes are available with many different characteristics. The three main types are referred to as passive high-impedance, active high-impedance, and passive low-impedance.

Passive high-impedance probes usually range from as low as  $10\text{-k}\Omega$  to  $10\text{-M}\Omega$  load impedance. This number identifies the loading effect of the probe when attached to a circuit. The best feature of high-impedance probes is that their impedance is usually much larger that those of the circuit under test and thus do not present any appreciable DC-load to the measured signal when present.

Passive high-impedance probes do suffer one major drawback: significant capacitive loading. Most high-impedance probes present from 5 pF to 20 pF of capacitance at the probe tip. This capacitance affects measurements in two ways; it slows down the circuit being measured, and it degrades the rise-time of the probe. The upper bandwidth limit for passive high-impedance probes is around 400 MHz.

Active high-impedance probes combine a high bandwidth amplifier with the probe to improve the overall bandwidth of the system. These probes usually exhibit load impedances of 10 k $\Omega$  to 10 M $\Omega$  but have load capacitances of less than 3 pF. This type of probe has a typical upper bandwidth limit of around 1 GHz.

Care should be taken when using active probes as the manufacturers specified bandwidth may not be where the signal measured is 3 dB down. To achieve higher bandwidths, some active probes have non-linear responses to equalize the probe response. When presented with edge rates or frequency components beyond the specified probe bandwidth, the probe and scope may actually display a distorted waveform having more high-frequency components present than are actually in the measured signal.

Passive low-impedance (resistive divider or transmission line) probes are used for the highest frequency work. These probes are available in load impedances from  $50\Omega$  to  $5 k\Omega$ , and present load capacitances of 1 pF or less. A typical upper bandwidth limit for these probes is around 3 GHz. Unlike the high-impedance probes, low-impedance probes are de-

signed to connect to a  $50\Omega$  transmission line system and do not require compensation. The probe itself is an extension of the  $50\Omega$  transmission line present in the scope, and contains a precision resistive-divider at the probe tip.

The main drawback of passive low-impedance probes is the load impedance they present to the circuit. The rule of thumb for probes is that the probe impedance needs to be an order of magnitude greater than the impedances present around it to avoid any appreciable distortion. To get around this the probe is often designed as part of the system under test, such that its impedance is factored into the design. When the probe is not present it may be necessary to change component values or configurations to compensate for the absence of the probe (Reference 7).

Table 2 shows a summary of typical oscilloscope probe characteristics. For proper viewing of HOTLink ECL signals, an oscilloscope (and probes) should have a minimum system bandwidth of 720 MHz. In most cases this requires use of low-impedance probes.

**Table 2. Typical Probe Characteristics**

| Probe Type     | Z              | C <sub>load</sub> | BW (MHz) |

|----------------|----------------|-------------------|----------|

| Passive High-Z | 10 k–<br>10 MΩ | 5–20 pF           | 400      |

| Active High-Z  | 10 k–<br>10 MΩ | 3 pF              | 1000     |

| Passive Low-Z  | 50–5 kΩ        | 1 pF              | 3000     |

# Probe Grounding

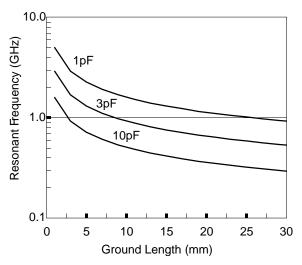

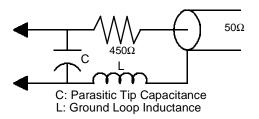

As with any measurement, a good ground is mandatory. What is often misunderstood is just what *is* a good ground. At the frequencies used with HOTLink, a long looping ground lead is about as good as no ground at all. Three factors come into play that degrade the signal: the reflections caused by the scope probe, and the ground inductance and parasitic capacitance limiting the probe's bandwidth. A simple rule of thumb for ground leads is that they exhibit about 1 nH of inductance for each millimeter of length. As the length of the probe's ground lead increases, the probe's resonance point decreases.

To view a signal with minimal distortion, the probe's resonant frequency must remain above the highest frequency signal component of interest. The graph in *Figure 7* shows how a scope probe's resonant frequency varies for different lengths of ground loop inductance and tip capacitance. This graph is based on Equation 3 with the diagram of a low-impedance probe shown in *Figure 8*.

$$\omega = 2\pi f = \frac{1}{\sqrt{LC}}$$

Eq. 3

From this graph it is quite apparent that a ground lead of only 10 mm cuts the resonant frequency of the probe by 75%. For signal viewing at HOTLink serial data rates it is usually necessary to use coaxial scope-tip sockets soldered directly to a circuit board, or some other probe type that probes for signal and ground without a loose ground lead (Reference 8).

Figure 7. Scope Probe Resonant Frequency

Figure 8. Scope Probe Tip Schematic

# Probing From V<sub>CC</sub>

The normal mode for probing ECL is to use  $V_{CC}$  as the ground reference. In this mode the signal being viewed is below ground and is relatively close to the ground reference. If the overall circuit design uses TTL parts in a mix with the negative referenced ECL, the TTL signals all exist above ground. If the ECL parts are operated in a PECL mode where they share a common  $V_{CC}$  supply with other TTL or CMOS parts, all probing should be done from TTL ground, which is the  $V_{EE}$  side of the ECL parts.

# Probing From V<sub>EE</sub>

When  $V_{\text{EE}}$  is used as the scope ground, other issues may come into play. In this mode the ECL signal is now positioned almost 4V above the reference level. While many scopes are able to perform a DC offset to make the ECL signal viewable, some do this at the expense of sensitivity. In other words, a signal that is viewable at 100 mV/div when offset less than 2V, may only be viewable at 500 mV/div when offset by 4V. Since the total signal swing for ECL signals is only 800 mV, it may be difficult to see a detailed representation of the waveform at this resolution.

Another problem with measuring from  $V_{EE}$  is that all the references in the ECL part are regulated from  $V_{CC}$ , not  $V_{EE}$ . This means that any amplitude changes or ripple in the power supply are now added into the displayed waveform.

One way around the offset problem is to AC couple the signal into the scope. Some scopes offer this as a front panel set-up

selection, while others require the addition of a wide-bandwidth DC-blocking capacitor in-line with the scope probe. Either of these remove all DC components from the signal under test, and allow the signal to be displayed at the maximum resolution of the oscilloscope.

Wide-bandwidth capacitors designed for this function are available from most test equipment manufacturers for use with existing probes and scope amplifiers. Some common capacitor types for SMA connector probes are the Tektronix 015-1-13-00 and Hewlett-Packard 11742A. For BNC connectored probes the Hewlett-Packard 10240B is also available.

### Sample ECL Waveforms

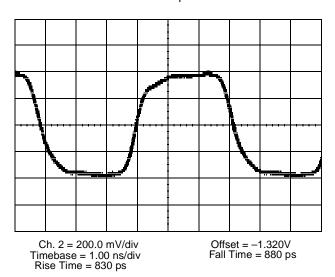

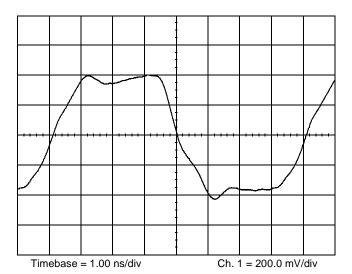

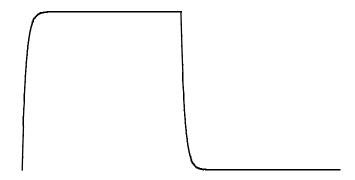

ECL signals, when properly biased, terminated, and bypassed, are very clean and stable. Any noticeable overshoot on signals is usually caused by reflections from improperly terminated transmission lines or improper probing. *Figure 9* shows what a pristine single-ended ECL waveform should resemble when viewed on a scope.

Figure 9. Good ECL Waveform, Single-Ended vs. V<sub>CC</sub> Ground

Both the rising and falling edges are quite symmetrical and approximate an RC charge/discharge curve. The peak-to-peak range of the transition covers approximately 800 mV and is centered around  $V_{CC}-1.3V$ . This signal was measured using a  $500\Omega,\,1.5\text{-GHz}$  bandwidth low-impedance probe, on a scope having 1-GHz bandwidth, with  $V_{CC}$  as the probe ground. The probe load impedance ( $500\Omega$ ) was combined with other bias resistors to present a  $50\Omega$  to  $V_{CC}-2V$  load on the signal.

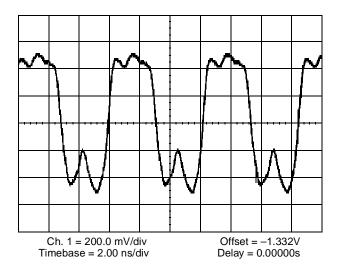

With incorrect termination, a waveform such as that in Figure 10 can result. Here the spike in the middle of a low area may cross the receiver  $V_{IH}$  threshold and cause the receiver to start to switch.

# **ECL Logic Families**

Just as the TTL compatible world has its 7400, 74LS, 74H, 74S, 74AS, 74ALS, etc. logic families that have evolved over time, so does ECL. The most common families still in use are referred to as 10K (e.g., SL10104), 10KH (e.g., MC10H116), and 100K (e.g., F100150). These ECL families differ in terms

Figure 10. Bad ECL Waveform

of speed, signal levels, noise margins, and temperature and voltage stability.

#### 10K ECL

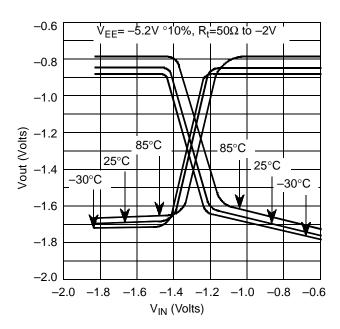

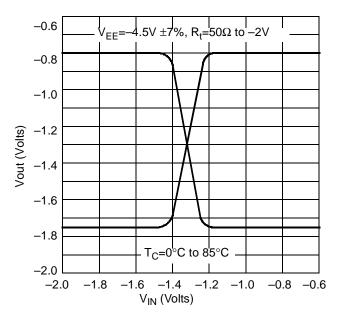

The 10K ECL family has been around since 1971. It provides propagation delays of 2 ns with slow 3.5-ns edge rates (10%–90%). The voltage swings and switching thresholds of this logic family are relatively insensitive to variations in the power supply voltage but are affected by operating temperature (–30°C to +85°C). The  $V_{BB}$  bias network is fixed at  $V_{CC}$  – 1.29V, and is compensated for voltage and temperature. In the basic 10K ECL switch the current source is unregulated and consists of a single resistor between  $V_{EE}$  and the tied emitters of the differential amplifier. The transfer curves of a simple 10K gate are shown in Figure 11 and detail how this family is sensitive to temperature variations in both inputs and outputs (Reference 19).

#### 10KH ECL

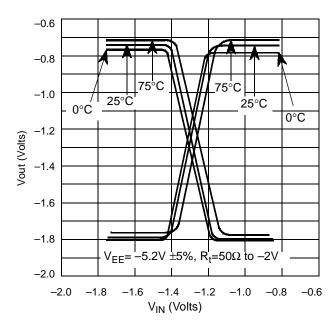

To improve system speeds, the 10KH ECL family was introduced in 1981. It reduced propagation delays to 1 ns while edge rates were set to 1.8 ns. Because the thresholds and voltage swings remain the same in 10KH as in 10K, these two ECL families are fully compatible with each other. The temperature- and voltage-compensated V<sub>BB</sub> reference network from 10K parts was replaced with a fully compensated and regulated supply. To improve the V<sub>OL</sub> levels, the resistor current source was replaced with a regulated current source. This allowed the collector resistors in the ECL switch to be matched and have similar switching characteristics. The transfer curves of a simple 10KH gate (see Figure 12) illustrate how this family improves noise margins over 10K ECL, yet remains sensitive to temperature variations. The 10KH family also is specified to operate over a narrower temperature range (0°C to 75°C) than 10K ECL (Reference 19).

# 100K ECL

The 100K ECL family is a faster and easier to use ECL logic family. Introduced in 1973, this family improved on the internal structures to provide 750-ps propagation delays and 1-ns edge rates. In addition to speed improvements, the 100K ECL family was the first to introduce full compensation. This

Figure 11. 10K ECL Transfer Functions

Figure 12. 10KH ECL Transfer Functions

means that all the critical structures in the parts are now compensated for variations in voltage and temperature. This minimizes differences in propagation delays from one stage to the next that limit the maximum operating rate of a system. This stability is illustrated in the transfer curves in *Figure 13* (Reference 5).

In the 100K ECL family the operating temperature range is expanded to  $0^{\circ}$ C to  $85^{\circ}$ C but the nominal operating voltage changes from -5.2V to -4.5V.

Figure 13. 100K ECL Transfer Functions

# **HOTLink ECL Outputs**

All ECL outputs of the HOTLink Transmitter are ECL 100K-level compatible. This means that these outputs meet or exceed all voltage, current, and edge rates specifications of 100K ECL and will interoperate with other 100K ECL parts. This signal level compatibility is required by the ANSI Fibre Channel standard (Reference 3).

The HOTLink ECL outputs actually are substantially better than the 100K ECL specification, allowing operation with 5V±10% supplies over the full -55°C to +125°C temperature range. This allows the HOTLink parts to be used in TTL, PECL, or ECL environments.

The HOTLink Transmitter has six ECL outputs configured as three differential pairs: OUTA±, OUTB±, and OUTC± (see Figure 2). These differential outputs may be used to communicate with ECL-compatible receivers in either single-ended (strongly discouraged) or differential (preferred) modes.

#### HOTLink Transmitter Single-Ended Connections

A single-ended connection is used most often for logic functions. In this type of a connection, a single output of a driver is attached to a single input of a receiver. The receiving element is thus dependent on the driver and interconnect for maintaining the input signal in the narrow voltage bands specified for a valid logic 1 or 0.

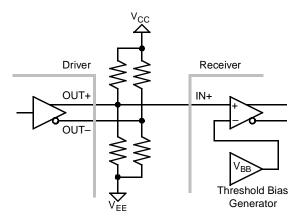

Figure 14 illustrates the basic components of a single-ended connection. The driver differential pair outputs are biased to allow them to switch. The receiver, as with all ECL gates, is based on a differential amplifier. In the case of a single-ended receiver, the second input into the differential amplifier is not present at an external pin on the chip, but is instead connected internally to a  $V_{BB}$  reference voltage. The receiver switches as the signal present on IN+ goes either above or below the internal threshold set by  $V_{BB}$ .

While connections of this type are perfectly fine for logic functions, they should be avoided for a communications link. In a single-ended environment, any signal level differences

Figure 14. Single-Ended Connection

(caused by temperature, logic family, transients, power supply noise, etc.) directly affect the received signal timing. In a logic function this timing variation limits a design both in determining how fast the system may operate, and in how much noise margin is present.

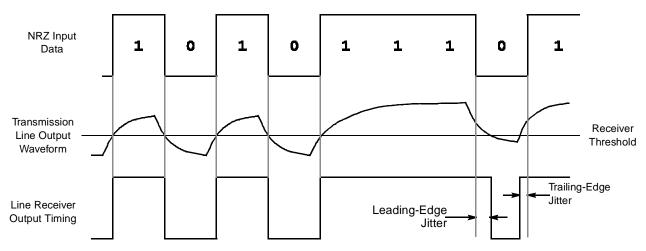

In a communications link these variations in timing translate directly into jitter in the serial data stream. Jitter affects a serial link by limiting not only how fast the link can operate (data rate) but also how far the data can be sent. Jitter is discussed in detail later in this document.

The only expected single-ended connection on a HOTLink Transmitter is for a local loopback function to a HOTLink Receiver (when the INB— input is not available for a differential connection because it has been used as an ECL-to-TTL translator). In this connection it is expected that the transmitter and receiver are in relatively close proximity, such that the connection between them is more on the order of a logic connection than a communications link. The small amount of jitter caused by the single-ended connection will be far below the jitter susceptibility of the HOTLink Receiver.

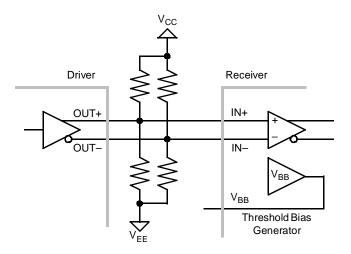

### HOTLink Transmitter Differential Connections

A differential connection is the preferred attachment for HOTLink Transmitter serial outputs. In a differential connection both outputs a of a driver are connected to the true and complement inputs of an ECL-compatible receiver. When connected in this fashion the majority of the interconnect dependencies are removed. The main advantages of a differential connection are insensitivity to the logic family, operating temperature, and power supply variations. In addition, the connection is now immune to most common-mode noise.

Figure 15 shows the basic components of a differential connection. The driver differential pair outputs are biased to allow them to switch. Now both true and complement inputs of the receiver differential amplifier are available at external pins and are connected to the complementary outputs of the driver.

Some ECL differential receivers may also provide an external  $V_{BB}$  reference. This reference is provided for those cases where a driver is connected single-ended to one of the differential receiver inputs. The other receiver input must then be connected to the  $V_{BB}$  reference to allow the receiver to switch. With a true differential connection this  $V_{BB}$  output should remain open.

Figure 15. Differential Connection

The main concerns in a differential connection are signal skew and crosstalk. Skew is the difference in arrival time of the OUT+ and OUT- signals at the receiver. Crosstalk is the coupling of energy into these same two signals.

As the amount of signal skew present in a differential connection is increased, the effective signal rise and fall times at the differential receiver also increase. In systems with large amounts of signal skew, it is possible for short pulses to never be detected by the receiver.

The main cause of signal skew is asymmetric routing of the true and complement signals between the driver and the receiver. A 1-inch difference in routing length is equal to about 150 ps of signal skew. This problem is corrected by maintaining matched signal runs between the HOTLink Transmitter and the ECL differential receiver.

The main cause of crosstalk is long parallel traces carrying other signals. The adjacent lines act as coupling transformers and transfer energy from one to another. One cure for this is to limit the length of the connection by placing the ECL differential receiver as close to the HOTLink Transmitter as possible. Other possibilities are to route the differential signals between the power planes as stripline. If routing is to remain on the same plane, the crosstalk effects can be minimized by horizontally separating the adjacent signals as far as possible or by routing a ground trace (with many vias to attach the ground trace to the ground plane) between the signals.

#### **HOTLink ECL Inputs**

The ECL inputs on the HOTLink Receiver are also ECL 100K-level compatible. Similar to the transmitter, these inputs have also been enhanced to operate over a wider range than standard 100K ECL.

The differential INA $\pm$  and INB $\pm$  inputs offer improved minimum sensitivity of 50 mV, compared to 150 mV for the few 100K ECL differential receivers available. These inputs may be connected directly to either power rail without damage to the part, or changing the internal thresholds of other sections of the receiver. These same differential inputs also operate with a 3V common-mode rejection range (V<sub>CC</sub> down to V<sub>CC</sub> – 3V) that is twice the 1.5V range of standard 100K ECL differential receivers (V<sub>CC</sub> – 0.5V down to V<sub>CC</sub> – 2V).

**Note**: While differential outputs are quite common on ECL parts, true differential inputs are rare. The most common usage for differential inputs is on line receivers and clock drivers. The common-mode range on some parts with differential inputs is quite limited and should not be expected to operate over even a narrow range unless explicitly stated in the manufacturer's data sheet.

The INA $\pm$  inputs of the HOTLink Receiver should always be connected to a differential signal source. Since there is no V<sub>BB</sub> reference output on the receiver, there is no way to properly bias the second input of the differential receiver.

The INB± inputs may be configured to operate either as a differential receiver (in which case it should be connected to a differential signal source) or as two single-ended receivers. When operated as two single-ended receivers (as configured using the SO pin) the INB+ input operates as a 100K ECL single-ended receiver for serial data, while the INB–(SI) input operates as a 100K ECL single-ended receiver for an ECL-to-TTL level translator. The V<sub>BB</sub> reference for these signals is available only inside the HOTLink Receiver and is not brought to an external pin. Signals connected to these single-ended inputs must now ensure operation within the 100K threshold levels.

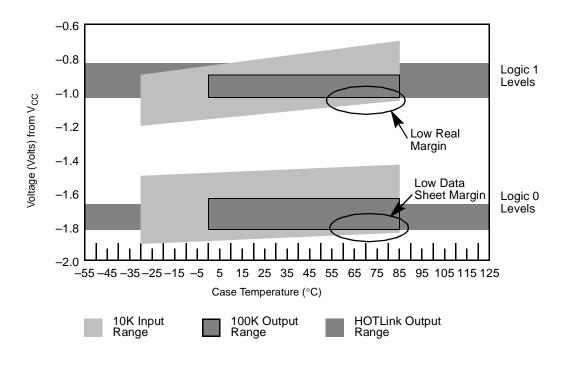

# Mixing ECL Logic Families

It is often desirable to use ECL parts of different families together in the same design. This can be done if certain rules are followed. The main reasons for these rules are the variability in signaling levels in ECL 10K family parts. *Figure 16* shows a DC-level comparison for 100K ECL outputs driving single-ended 10K ECL inputs.

In this configuration there is only 20 mV of margin between the 100K  $V_{OHL}$  and the 10K  $V_{IH}$  at the upper end of the temperature range. With 10K parts driving other 10K parts (assuming a common operating temperature) this is not a problem as the internal reference in each part follows a similar temperature shift. If the case temperature of the receiving 10K part can be kept below 35°C (100 mV margin), it can safely be used with 100K ECL parts for logic functions.

While the  $V_{OLH}$  specification appears to also have a noise margin problem, it does not. What occurs here is a condition where the receiver may be operated outside its linear region; i.e., 1s and 0s are detected properly but the timing response may not match the manufacturer's data sheet.

Figure 17 shows the opposite configuration with 10K ECL logic driving either a single-ended 100K ECL receiver or a HOTLink Receiver. Here there are no tight margin areas between input and output thresholds. This means that 10K ECL parts can safely be used to drive 100K ECL inputs over their full temperature range.

Figure 17 also highlights the enhanced input range for the HOTLink Receiver. Unlike the narrow input range present on standard ECL families, the ECL inputs on the HOTLink Receiver maintain normal operation over the entire  $V_{CC}$  to  $V_{CC}-3V$  range.

Figure 16. 100K ECL Driving 10K ECL

Figure 17. 10K ECL Driving 100K ECL

### Single-Ended Connections

Both of these comparisons are based on single-ended connections, where only a single ECL output is used to drive the receiving internally-referenced single-ended gate. In these cases, the other input to the receiving differential amplifier is connected internally to a  $V_{BB}$  reference. This type of connection should not be used to drive the INA± or INB± differential inputs of the HOTLink Receiver.

#### Differential Connections

One of the biggest advantages of ECL is the ability to communicate in a differential mode. This mode is relatively rare on logic parts (most commonly used for clock drivers and line receivers), as it requires both the driving and receiving parts to have both true and complement outputs and inputs respectively. When connected in this manner, the receiving part is no longer comparing the input signal to its  $V_{BB}$  reference, but instead compares the true and complement inputs to each other.

When used in this mode there is no problem using 100K ECL with 10K ECL at any temperature. Because an ECL receiver only requires around 250 mV of difference to fully switch, and the difference between the outputs of a differential driver remains near 800 mV, any differential connection has a minimum of twice the noise margin of a single-ended connection.

This type of connection is also immune to minor differences in the reference voltages between parts. Because the connection is differential, any common-mode voltages present on the received signals (due to power supply differences, AC coupling, ground shift, etc.) within the common-mode range are canceled out in the receiving differential amplifier. Some ECL parts with differential inputs can accept up to 1V of common-mode offset on the received signal without degradation of performance. The enhanced 100K ECL compatible inputs of the HOTLink Receiver can accept inputs between  $V_{\rm CC}$  and  $V_{\rm CC}-3V$ , offering a common-mode range of 3V.

# **HOTLink Transmitter Connections**

Unlike conventional negative-referenced ECL, the high-speed outputs on the HOTLink Transmitter are implemented in 100K positive-referenced ECL (PECL). This allows the TTL and ECL interfaces on the transmitter to operate from a common +5V power supply.

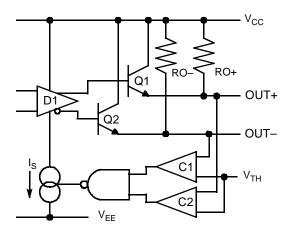

The HOTLink Transmitter has three differential output sections: OUTA±, OUTB±, and OUTC±. In addition to operating as 100K ECL-compatible signals, these outputs have been enhanced with additional features.

#### **Power Saving Mode**

A standard ECL output structure uses a constant current source at the base of a differential amplifier (see *Figure 5*). In these standard parts, this current source is enabled and dissipating power even when the outputs are not used.

The HOTLink Transmitter ECL outputs, while still operating as true 100K ECL outputs, incorporate some additional structures (see *Figure 18*) to save power when the outputs are not used. The differential amplifier (D1) under normal conditions directs the  $I_S$  current from the current source through its internal transistors. As this current is switched, the output driver transistors (Q1 and Q2) change their operation point and the amount of current they source (a properly biased ECL output sources current in both 1 and 0 states; i.e., it never enters

cutoff). Each output driver (Q1 and Q2) contains a high value pull-up resistor (RO+ and RO–) and a voltage comparator (C1 and C2).

Figure 18. HOTLink Transmitter ECL Output

When both voltage comparators of a HOTLink differential output detect a voltage above a 100K ECL output-high level ( $V_{TH}$ ), the current source ( $I_{S}$ ) for that differential output pair is disabled. This results in a current savings of around 5 mA (25 mW) for each unused output pair.

# **FOTO Control of OUTA± and OUTB±**

The HOTLink Transmitter OUTA± and OUTB± differential outputs have an additional control input not present in the OUTC± output pair. While the OUTC± outputs are always enabled to follow the serial data stream generated in the HOTLink Transmitter shifter, the OUTA± and OUTB± outputs are not. These outputs are also controlled by a TTL-level input called FOTO (fiber-optic transmitter-off). While OUTA± and OUTB± are disabled, the OUTC± pair remains active and can be used for a local loopback source.

This FOTO signal is used to force the differential outputs of the OUTA± and OUTB± drivers to a state where a logical 0 is being driven. This state corresponds to a condition on optical modules where no (or minimal) light is transmitted. While not required for LED-based optical modules, this capability may be required for laser-based links (see ANSI Z136.1 and Z136.2, F.D.A regulation 21 CFR subchapter J, and IEC 825) (References 9, 10, 11, 12, 13).

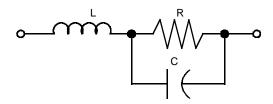

# **ECL Output Biasing**

ECL outputs have specific loading requirements to ensure proper operation. Because of the open-emitter structure of an ECL output, it can source current but cannot sink current. To allow the output to switch, some form of pull-down is required on the output. This pull-down usually takes the form of a resistive load; either to  $V_{\text{EE}}$  or  $V_{\text{CC}}-2V$ .

Most ECL outputs are specified for driving load impedances as low as  $50\Omega$ . Because an ECL output does not swing rail-to-rail, this load is usually specified at  $V_{CC}-2V$ , a point slightly below the ECL  $V_{OL}$ . At this point, when the ECL gate is driving a logic-0 signal, a small current is running through the load resistor to keep the output transistor in the active region. Typical currents sourced when driving a logic-1 ( $I_{OH}$ ) and logic-0 ( $I_{OL}$ ) are calculated using Equations 4 and 5 re-

spectively, where  $R_T$  is the effective load impedance and  $V_{TT}$  is the effective bias voltage.

$$I_{OH} = \frac{V_{OH} - V_{TT}}{R_t} = \frac{(-0.9) - (-2.0)}{50\Omega} = 22 mA$$

Eq. 4

$$I_{OL} = \frac{V_{OL} - V_{TT}}{R_t} = \frac{(-1.7) - (-2.0)}{50\Omega} = 6mA$$

Eq. 5

These  $I_{OH}$  and  $I_{OL}$  values are the basis for the timing and signal levels in the HOTLink data sheet. For other values of  $I_{OH}$  and  $I_{OL}$ , the transmitter exhibits slightly different characteristics. These current flows can be achieved in many ways. The four most common methods are:

- Shunt bias to V<sub>TT</sub> bias voltage

- Shunt bias to V<sub>EE</sub> bias voltage

- Thévenin bias to V<sub>TT</sub> bias voltage

- Y-bias to V<sub>TT</sub> bias voltage

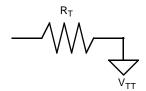

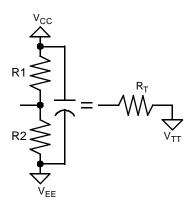

### Shunt Bias to V<sub>TT</sub>

In shunt bias, as shown in *Figure 19*, a single resistor is used as a pull-down load on an ECL output to some bias voltage. When biased to  $V_{TT}$ , a single  $50\Omega$  resistor  $(R_T)$  from the ECL output to  $V_{TT}$  is all that is necessary. This type of biasing requires an additional power supply to provide the  $(V_{CC}-2V)$   $V_{TT}$  level. This bias type dissipates the least average-power (13 mW) of any output load type. It is often used in large ECL systems, in systems where overall power dissipation is a major concern, or where there is enough ECL present to warrant its design and implementation.

Figure 19. Shunt Bias to V<sub>TT</sub>

# Shunt Bias to V<sub>EE</sub>

ECL outputs may also be biased to the  $V_{EE}$  supply as shown in *Figure 20*. Here a load resistance ( $R_T$ ) of around 270 $\Omega$  is connected to the  $V_{EE}$  supply to provide a similar current load for the ECL output driver. This value is determined by taking the average current flow for both a 1 and a 0, at the midway point ( $V_{BB}$ ) in the output swing. The calculation for this is shown in Equation 6.

Figure 20. Shunt Bias to  $V_{\text{EE}}$

$$R = \frac{V_{EE} - V_{BB}}{\frac{I_H + I_L}{2}} = \frac{5 - 1.3}{\frac{22 + 6}{2}} = 264\Omega$$

Eq. 6

Unlike the shunt bias to  $V_{TT}$ , this bias arrangement dissipates a significant amount of power in both the 1 and 0 states (47 mW average). This bias type (due to mismatched RC charge and discharge rates) exhibits a faster falling edge than rising edge. Because of this, its use is usually limited to logic functions, and is discouraged for serial links and for biasing differential output pairs. This is discussed in detail later in this document.

# Thévenin Bias to V<sub>TT</sub>

In a Thévenin bias network, a pair of resistors (R1 and R2) are used to create a load whose Thévenin equivalent matches that of a single resistor attached to a specific bias voltage ( $V_{TT}$ ). For ECL this voltage is usually  $V_{CC}-2V$ . These resistors are connected as shown in *Figure 21*. The values of R1 and R2 are solved using Equations 7 and 8.

$$R_1 = \frac{V_{EE} \times R_T}{V_{EE} - V_{TT}}$$

Eq. 7

$$R_2 = \frac{V_{EE} \times R_T}{V_{TT}}$$

Eq. 8

Figure 21. Thévenin Bias Equivalent

Solving for  $50\Omega$  and  $V_{CC}-2V$  yields values of  $83\Omega$  and  $125\Omega$  for a 5V system. While this combination does provide a similar dynamic load to the shunt bias to  $V_{TT}$ , it dissipates nearly an order of magnitude more power (138 mW) than its shunt to  $V_{TT}$  equivalent.

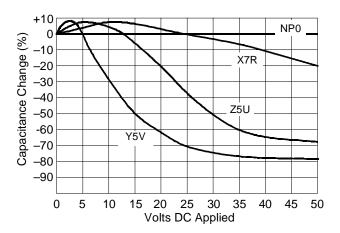

The capacitor shown in *Figure 21* is needed to allow R1 and R2 to provide the proper load for AC signals. In a Thévenin equivalent circuit, the power supply is assumed to be a short circuit. While this may be accurate for DC or very low frequency AC signals, the power supply appears as a near infinite impedance at RF frequencies. The bypass capacitor across R1 and R2 is used to create an AC short. This capacitor must be sized to operate as a short near the frequencies in use. For HOTLink-based systems this capacitor should probably be in the range of 300 pF to 0.01  $\mu$ F.

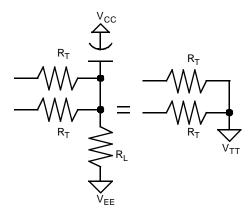

# Y-Bias to V<sub>TT</sub>

Unlike the three previously described bias configurations, the, Y-bias can only be used with differential outputs. In this configuration the current from both ECL outputs are summed together through a single load to  $V_{\text{EE}}$ . Since the net sum of these currents remains constant as the output switches, the

voltage drop across this load remains constant. A schematic of this bias network is illustrated in *Figure 22*.

Figure 22. Y-Bias Network

Here  $R_T$  is the desired load impedance, usually  $50\Omega$  to  $V_{CC}-2V$  for ECL systems.  $R_L$  is determined by summing the currents of a logic 1 and a logic 0 (as shown in Equations 4 and 5), and calculating the resistance necessary to drop the remaining voltage. This calculation is shown in Equation 9 and solved for a  $50\Omega$   $R_T$ .

$$R_L = \frac{V_{CC} - V_{EE} + V_{TT}}{I_{HI} + I_{LOW}} = \frac{3V}{28mA} = 107\Omega$$

Eq. 9

This type of bias provides a significant power savings over a Thévenin bias because only a single pull-down resistor is used to dissipate power for two outputs. For a  $50\Omega$  equivalent load the power dissipation is only 110 mW for two outputs (55 mW for one). Just as with the Thévenin bias, a capacitor is necessary to create an AC short.

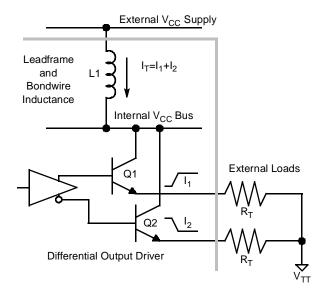

#### **Matched Loading**

Just as the differential amplifier in an ECL switch directs current flow, so do the emitter-follower output transistors. As these transistors are turned on an off, large amounts of current are switched through the driver's  $V_{CC}$  package pins. Because of the inductance present in these pins, transients can be induced in the internal  $V_{CC}$  supply.

Fortunately the effects of this lead-inductance only manifest themselves when the current through the  $V_{CC}$  supply pin changes. If the current is kept stable, no transients are induced. Due to the differential configuration of many ECL outputs, it is possible to keep this current stable by having matched loads on the true and complement outputs of the differential driver. This means that if a design uses either one or both outputs of a differential driver, they both should drive loads of the same magnitude.

Figure 23 shows a differential output driver connected to a load including the package inductance present on the  $V_{CC}$  power pin. As the differential driver changes state, the overall current through L1 remains the same (assuming that both  $R_T$  loads are the same value).

Figure 23. Loaded Differential Driver

If one of the two  $R_T$  load resistors is removed, some very undesirable things start to happen. First, the external power supply must now react to a dynamic rather than a static need for current. This increases the amount of power-supply bypassing that is needed next to the ECL driver  $V_{CC}$  pin. The second is a variation in the internal and external  $V_{CC}$  supplies caused by the dynamic current flow. This effect is examined in the following approximation.

For a single ECL output the current difference from a logic 1 to a logic 0 (into a  $50\Omega$  to  $V_{CC}-2V$  load) is 16 mA (see Equations 4 and 5). The ECL 100K family data sheets document that signal transition times may be under 500 ps. By assuming the rise and fall portions of the signal are related to a triangular waveform, this transition may be roughly converted to a fundamental frequency using Equation 10.

$$F = \frac{1}{2 \times T_r} = \frac{1}{2 \times 500 \text{E}^{-12}} = 1 \text{GHz}$$

Eq. 10

The Fourier series for a triangular waveform is listed in Equation 11. This illustrates that most of the energy content is present at the fundamental frequency with much smaller components present at the higher odd harmonics. To simplify the following calculations only the fundamental frequency is assumed to be present (Reference 24).

$$\frac{8V}{\pi^{2}} \left(\cos \omega_{0} t + \frac{1}{9} \cos 3\omega_{0} t + \frac{1}{25} \cos \omega_{0} t + \dots\right)$$

Eq. 11

If a package pin inductance of 4 nH is assumed (typical for many surface mount components), Equation 12 can be used to determine the impedance of the package at this frequency.

$$X_L = 2\pi F L = 2\pi \times 1E^9 \times 4E^{-9} = 25\Omega$$

Eq. 12

Using Ohm's Law we can now convert this change in current into an internal voltage change, as illustrated in Equation 13.

$$V = I \times X_L = 16mA \times 25\Omega = 400 \, mV$$

Eq. 13

This temporary difference between the internal  $V_{CC}$  and the external  $V_{CC}$  supply is the same phenomenon known in a TTL environment as ground bounce.

All of this, of course, is based on the assumption that the output is able to switch at this speed (500 ps) and provide the specified current (16 mA) when presented with a high-impedance source. What actually occurs is that the output edge slows down to match the current transfer permitted by the on-resistance of the output driver transistor and the package reactance.

Most ECL parts use a couple of different techniques to combat this problem. Both are quite simple to implement. The first is to use a separate package pin to provide power to the emitter-follower output transistors. This prevents any  $V_{CC}$  shift caused by the output drivers from affecting the sensitive differential amplifiers and voltage references present in other parts of the device.

The second method is to maintain a balanced load on the differential output drivers. Since the rising and falling edge rates of ECL are very symmetrical,  $\Delta I_1 = \Delta I_2$ . Because these changes in output current are symmetrical,  $\Delta I_T \cong 0$ . From Equation 13 we know that any induced  $\Delta V$  is directly proportional to  $\Delta I$ ; thus as  $\Delta I$  goes to 0, so does  $\Delta V$ .

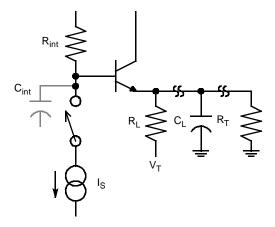

### **AC Characteristics of Output Drivers**

In an ECL driver, the time it takes for the signal to rise is largely determined by its internal resistors and parasitic capacitors (C<sub>int</sub> and R<sub>int</sub> in *Figure 24*), since the emitter-follower can supply large currents to charge the load capacitance. The DC voltage to which the output rises is determined by the emitter-follower transistor characteristics and the internal driver resistor (R<sub>int</sub>) value. However, the AC voltage (overshoot, ringing, etc.) is determined primarily by the load characteristics. A capacitive load (along with the inductance found in the package, printed circuit traces, and other load components) causes the output to rise significantly beyond the anticipated DC output level, since the emitter-follower cannot supply any compensating current at the top of its transition.

Unlike the output rise time, the fall time is primarily determined by the time constants of the load capacitance and pull-down circuit. The output LOW voltage ( $V_{OL}$ ), is determined by  $R_{int}$ ,  $I_{S}$ , and the characteristics of the emitter-follower transistor. In a properly designed system the load circuit has time constants comparable to (or shorter than) the internal fall time, such that the emitter-follower can source a small amount of current during the entire time it is switching from HIGH to LOW. If this is not true, the emitter-follower transistor will be shut off for part of the transition time, and the output will follow the time constant of the load.

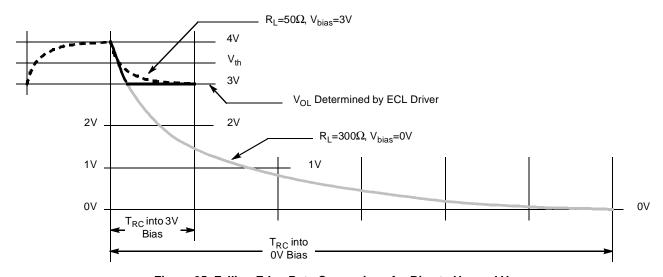

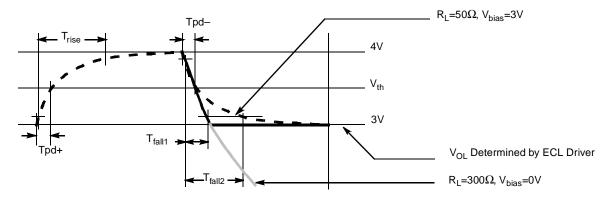

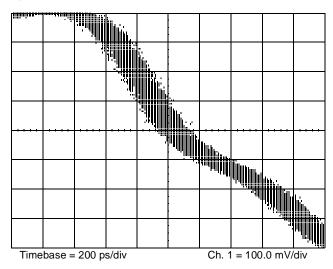

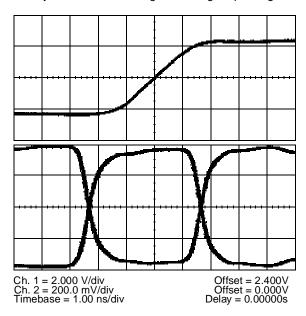

Figure 25 illustrates the effects of two different load or bias circuits. The assumption in both of these examples is that the load circuit controls the fall time of the signal, and that the pull-down current is being supplied by a resistor to a  $V_T$  of either  $V_{CC}-2V$  or  $V_{EE}$  (+3V or ground for a PECL environment). In the dashed curve, the standard ECL load of  $50\Omega$  to  $V_{CC}-2V$  is used, causing an output current of approximately 20 mA when the output is HIGH, and 5 mA when the output is LOW. This load (or its equivalent) can be created using all of the previously described bias networks except shunt the bias to  $V_{FE}$  (shown in the solid curve).

Figure 24. ECL Output Driver with Loading

Figure 25. Falling Edge Rate Comparison for Bias to  $V_{TT}$  and  $V_{EE}$

Figure 26. Expanded Detail of Falling Edge Rate Comparison

The same amount of pull-down current can be realized with a single resistor (R<sub>L</sub> in *Figure 24*) in a shunt bias to V<sub>EE</sub> configuration. To get a comparable output current (and assure comparable voltages at the output) the pull-down resistor is chosen to sink approximately the average of I<sub>OH</sub> and I<sub>OL</sub> when connected to a voltage midway between V<sub>OH</sub> and V<sub>OL</sub> (see *Equation 6*). The I<sub>OH</sub> and I<sub>OL</sub> currents listed here yield a pull-down resistor of around  $300\Omega$ . This type of bias is perfectly correct and adequate for ECL logic circuits where the mismatch between rise and fall times is absorbed into the normal logic delays and set-up times. In a data transmission system the effects of this type of output bias can be unpredictable and will often degrade performance.

Figures 25 and 26 illustrate the difference in output fall time assuming a constant load capacitance, with the only variation being the bias resistor and voltage. The  $50\Omega$  load resistor (dashed line) follows an RC discharge curve which ends at  $V_{CC}$  – 2V. For normal loading this *soft* edge rate more closely matches the rise time of the output as controlled by the emitter-follower, and is less affected by variations in load capacitance and reflection currents.

The  $300\Omega$  load resistor (solid line) follows an RC discharge curve which would normally end at  $V_{EE}$  (ground). While this appears to have a crisper edge rate, it is more severely affected by load capacitance variation and transmission line reflection currents that must be accommodated.

Figure 26 shows that with either pull-down the total voltage swing is the same, and is determined by the internal voltage swing of the driver, as buffered by the emitter-follower transistor. While the RC curve for the  $300\Omega$  pull-down continues to  $V_{EE},$  the emitter-follower is turned on and sourcing current at the  $V_{OL}$  point and does not allow the output to continue farther down the curve.

In either configuration the signal delays match, since both falling edges cross the mid-swing line at approximately the same time, but the rise and fall times are different. These rise and fall times determine the higher frequency spectral components of the waveform. Differences in these spectral components affect the termination efficiency and waveform distortion caused by cable attenuation (Reference 14), and also effect the current distribution or "balance" on the output transmission line.

#### **Transmission Line Termination**

While often confused with ECL output biasing, termination of transmission lines is something quite different. Because of the reactive characteristics of transmission line termination, the resistors used for termination are often used as part of the output bias network, but they perform different functions.

Due to the high switching speeds of ECL, most of the interconnect between parts cannot be treated as simple connections. They must instead be treated as transmission lines. The distance between parts, in conjunction with the signal loading and rise and fall times, is used to determine at what point the interconnect must be treated as a transmission line. The general assumption is that short lines do not require termination, while long ones do. The determination of what is a long line is made using Equation 14 (Reference 5).

$$I \max = \frac{1}{2} \sqrt{\left(\frac{C_L}{C_O}\right)^2 + \left(\frac{T_I}{\delta}\right)^2} - \frac{C_L}{2C_O}$$

Eq. 14

The values for this equation for microstrip construction on G10/FR4 type board would be:

- I max maximum unterminated line length

- Tr source 20% to 80% rise time

- C<sub>L</sub> load capacitance (2 pF assumed for a load)

- $\delta$  delay per unit length (0.148-ns/inch)

- C<sub>O</sub> capacitance per inch

Running this calculation for various impedance and rise-time combinations yields the lengths listed in *Table 3*. Lengths beyond those listed here require termination.

Table 3. 100K ECL Maximum Unterminated Line Length (In Inches), Microstrip Construction

|                | Line Length (in inches) |           |        |  |

|----------------|-------------------------|-----------|--------|--|

| z <sub>o</sub> | 0.5 ns                  | 1 ns      | 1.5 ns |  |

| 50Ω            | 1.38                    | 3.06      | 4.74   |  |

| 62Ω            | 1.32                    | 2.99      | 4.67   |  |

| 75Ω            | 1.25                    | 2.91      | 4.59   |  |

| 90Ω            | 1.18                    | 2.82 4.50 |        |  |

| 100Ω           | 1.14                    | 2.76      | 4.44   |  |

The lengths listed in *Table 3* assume digital switching characteristics. The HOTLink ECL serial signals are, for the most part, analog in nature. This effectively shortens the maximum unterminated length. For HOTLink serial signals, any ECL trace greater than one inch (2.5 cm) in length should be terminated.

The objective of transmission line termination is to prevent reflection of power from the destination back to the source. This is accomplished by terminating the transmission line in its characteristic impedance ( $Z_{\rm O}$ ). The two basic types of line termination are referred to as series and parallel termination.

The actual amount of the source signal reflected is based on how well the line impedance matches the destination impedance. This determines how much voltage is reflected back into the transmission line. This ratio of reflected voltage to incident voltage is called the reflection coefficient  $\rho$  (rho) and is shown in Equation 15 (Reference 5).

$$\frac{V_r}{V_i} = \rho = \frac{R_T - Z_O}{R_T + Z_O}$$

Eq. 15

#### **Series Termination**

Series termination (sometimes referred to as source termination) requires that the load be high-impedance to properly operate. This type of line termination is **not** recommended for use with HOTLink because of the reactive nature of all parts at the high frequencies present on the HOTLink ECL signals.

#### **Parallel Termination**

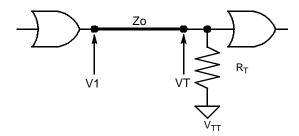

In parallel termination the desired characteristic is to terminate the *end* of the line (rather than the source) in its characteristic impedance. This results in a reflection coefficient of zero; i.e., no signal is reflected. This type of termination is implemented the same as shunt bias networks. *Figures 27* and *28* show the two equivalent forms of parallel termination.

Parallel termination offers the advantages of allowing distributed loads on the transmission line, and of having the termination network also operate as the bias network.

In the single-resistor form of parallel termination shown in Figure 27, the  $R_{T}$  resistor is sized to match the  $Z_{O}$  impedance of the transmission line. This termination form has the same advantage as the single resistor shunt bias because it dissipates less overall power than the Thévenin equivalent termination. It also has the same drawback of requiring a separate power supply.

Figure 27. Parallel Termination to V<sub>TT</sub>

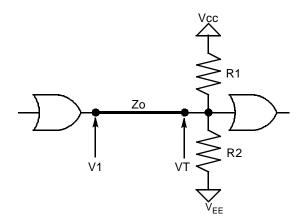

In a Thévenin equivalent termination (shown in *Figure 28*) two resistors (R1 and R2) are used to form an equivalent circuit to that in *Figure 27*. *Table 4* lists the R1 and R2 resistor val-

Figure 28. Thévenin Equivalent Parallel

ues for a number of common transmission line impedances. This table assumes operation with a 5V source and a termination voltage of  $V_{\rm CC}-2V$ , and selects the nearest standard 1% resistor value when an exact match is not available. These values are calculated using the same Equations 7 and 8 as used for calculating a Thévenin bias network (Reference 15).

**Table 4. Thévenin Bias Resistor Values**

| Z <sub>O</sub> | R1   | R2  |

|----------------|------|-----|

| 50Ω            | 82.5 | 124 |

| 70Ω            | 118  | 174 |

| 75Ω            | 124  | 187 |

| 80Ω            | 133  | 200 |

| 90Ω            | 150  | 226 |

| 100Ω           | 165  | 249 |

| 120Ω           | 200  | 301 |

| 150Ω           | 249  | 374 |

# **Terminating HOTLink Transmitter ECL Signals**

The HOTLink CY7B923 Transmitter has three different ECL differential output pairs named OUTA±, OUTB± and OUTC± (see *Figure 2*). How (or if) these outputs are terminated depends on what the output is used for.

# **OUTC**±

The OUTC± outputs of the HOTLink Transmitter are not controlled by the transmitter FOTO signal and are thus always enabled to drive serial data. While fully capable of driving either optical modules or copper cables, it is expected that the most common usage of this differential output will be as a local loopback to a HOTLink CY7B933 Receiver INB± inputs.

This signal may be connected to the HOTLink Receiver either differentially or single-ended. When connected differentially, the OUTC+ output is connected to the INB+ input, and the OUTC- output is connected to the INB- input. When connected single-ended, the OUTC+ output is connected to the INB+ input.

**Note**: For the INB+ input to be used differentially, the SI/SO ECL-to-TTL translator (mapped through the INB- input) must

be disabled. This is done by connecting the SO output directly to  $\ensuremath{V_{\text{CC}}}.$

Once the connection is made, the type of termination required is determined by the distance between the HOTLink Transmitter and the HOTLink Receiver. If the distance is kept short enough (under one inch) no termination is required and the output only needs to be biased (Reference 5). This can be done with a single pull-down resistor to V<sub>EE</sub>. While this type of termination does induce some jitter into the serial data stream (due to mismatched rise and fall times), the amount is well within the receiver limits.

If the distance is greater than one inch, the line should be terminated (Reference 5). To do this correctly requires determination of the characteristic impedance of the board traces used to connect the source and destination. Please see the Cypress Semiconductor application note "Driving Copper Cables with HOTLink" for information on how to determine the characteristic impedance of various types of transmission lines (Reference 16).

For local connections that do not travel through external transmission media (i.e., coax, twisted-pair, optical fiber, etc.) parallel termination may be used. The important consideration here is that both the OUTC+ and OUTC- outputs must be terminated/biased into the same size of load to maintain a current balance inside the HOTLink Transmitter.

If neither of the OUTC $\pm$  outputs are used, both outputs should be left open or pulled up to  $V_{CC}$  to disable the current source for the differential driver (see *Figure 18*).

#### **OUTA**± and **OUTB**±

The OUTA $\pm$  and OUTB $\pm$  outputs of the HOTLink Transmitter are both controlled by the FOTO signal which is required to meet laser safety regulations for communications links (References 9, 10, 11, 12, 13). Other than this special enable signal, these outputs operate the same as the OUTC $\pm$  outputs.

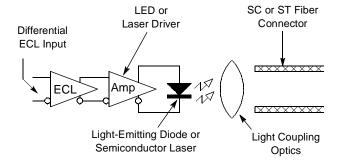

#### **Driving Optical Modules**

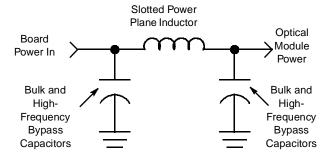

When connecting to optical modules, it is best to drive the optical module data inputs differentially. This provides the highest noise immunity for the system, and the lowest signal jitter. When used with *de facto* standard optical modules this becomes mandatory because the optical modules have a differential data input, yet do not provide a  $V_{BB}$  supply to bias the other input of the differential amplifier of the optical transmitter. Because this interface is intended for driving some external segment of optical cable, series termination (which uses shunt bias to  $V_{EE}$  and increases jitter) should not be used. Since the HOTLink parts are most probably be the only ECL parts in the system, the recommended termination is a Thévenin or Y-termination.

Both the Thévenin and Y-terminations provide the bias necessary for the ECL signal to switch, and the impedance necessary to terminate a transmission line. One of these types of termination/bias should be used even when the distance from the HOTLink Transmitter to the optical transmitter is short. This is necessary to maintain symmetrical rise and fall times for the OUTx± differential outputs.

#### PECL Optical Modules

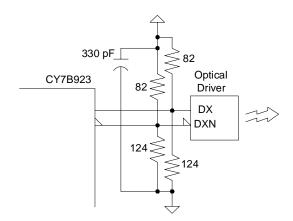

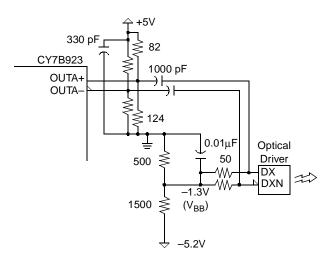

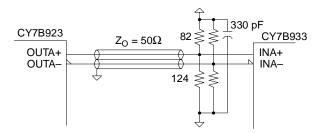

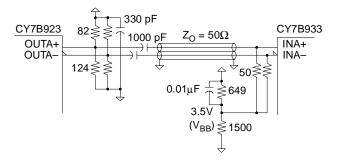

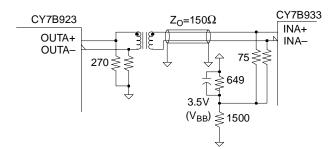

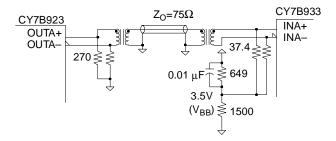

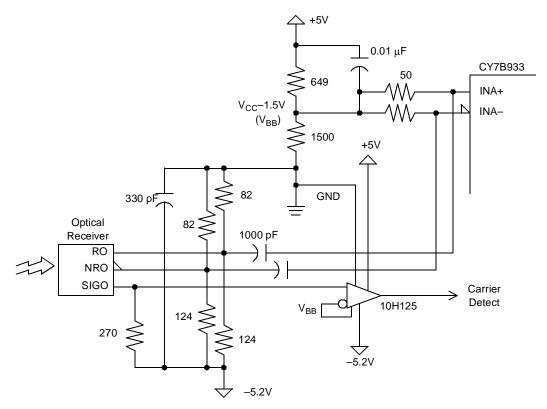

Interfacing to optical modules in PECL mode is quite simple, requiring only a few passive parts. The schematic in

Figure 29 illustrates the connections and parts necessary for this type of connection.

Figure 29. HOTLink Transmitter-to-PECL Optical Module

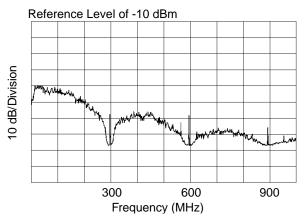

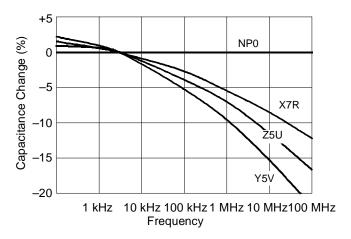

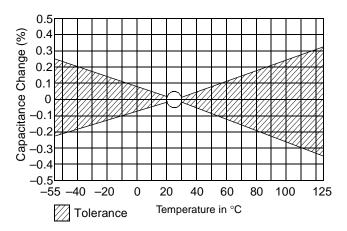

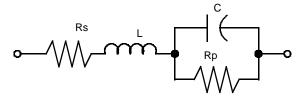

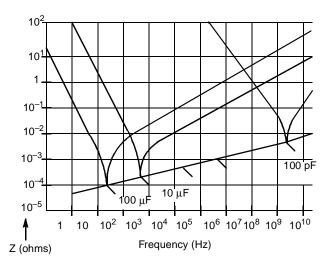

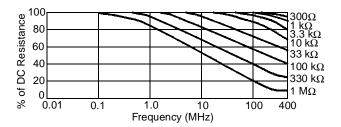

One of the key items often missed in this type of connection is proper bypassing of the termination/bias networks. The theory behind a Thévenin network is that the power supply is considered as a short for AC. While this may be true for near DC applications, the base frequencies and harmonics present in the HOTLink Transmitter output are far beyond any frequency the power supply itself could pass.

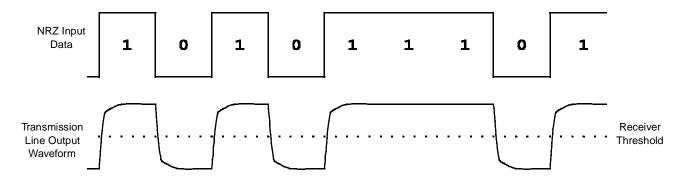

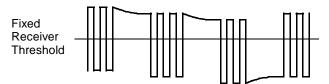

To make the power supply a short, a capacitor must be placed across the Thévenin pair. The size of the capacitor is determined by the frequency of operation of the serial link. A good rule-of-thumb is to pick the largest value capacitor whose series resonant frequency is 30% above the highest baseband frequency of the Baud rate of the serial data (Reference 17). Since the data is sent using an NRZ modulation (non-return-to-zero), the highest baseband frequency is one half the serial bit-rate (Reference 18).